400G ZR-QSFP-DD DCO-Module basieren auf DP- 16QAM, die ein erweitertes C-Band, eine kohärente Erkennung der Polarisation divers ität und einen fortschritt lichen elektronischen Verbindungs ausgleich unterstützen. Auf der Empfangs seite des Demodulators kann eine chromatische Dispersion kompensation angewendet werden. Dieses Modul wird unter Verwendung der Zwei-Draht-Schnitts telle verwaltet, die in der Common Management Interface Specific ation (CMIS) angegeben ist.

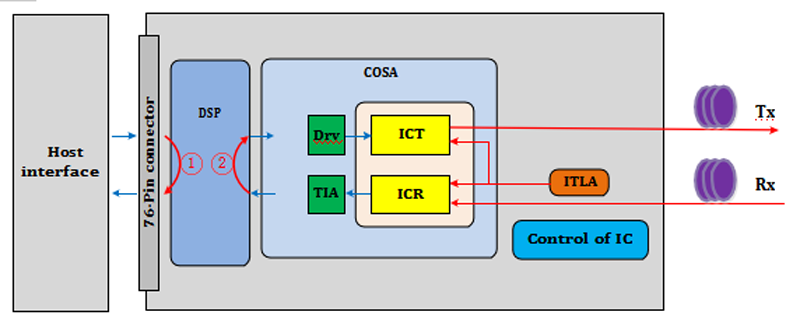

Das Modul verwendet einen 76-poligen QSFP-DD MSA-QSFP-DD Hardware spezifikation stecker für alle elektrischen Schnitts tellen mit der Host-Karte, während die optischen Schnitts tellen auf der Leitungs seite über die optischen Aufnahmen auf der QSFP-DD bereit gestellt werden. Das Modul kann in drei Funktions teile portion iert werden: TX-Pfad, RX-Pfad und Control & Power-Block.

Die Host-Schnitts telle besteht aus insgesamt 8 Hochgeschwindigkeits-SerDes-Bahnen. Auf diese Weise kann das Modul eine Schnitts telle für die 400-G-Anwendung unterstützen: eine unabhängige Client-Schnitts telle im doppelten 4-Spur-Modus (für 400GbE-Anwendung). und vier unabhängige Doppelspur-Modus-Client-Schnitts tellen (für 4 * 100GbE-Anwendung).

Die Verwaltungs kommunikation schnitts telle bietet eine Reihe von elementaren Verwaltungs operationen, mit denen der Host von Verwaltungs registern in Byte größe in der Verwaltungs speicher karte des Moduls lesen oder in diese schreiben kann. Es gibt Lese-und Schreib operationen sowohl für einzelne Bytes als auch für zusammenhängende Byte sequenzen. Es werden zwei Arten von Lese vorgängen unterstützt, entweder mit impliziter Adressierung (von der aktuellen Adresse gelesen) oder mit expliziter Adressierung.

Die Management-Kommunikation schnitts telle unter scheidet eine Rolle und eine s-Rolle. Der Host ist der und das Modul ist der s.

Das initiiert alle Operationen, die zur Daten übertragung führen. Daten können von den zu den s (in Schreib operationen) und von den s zu den (in Lese operationen) übertragen werden.

Merkmale

● Unterstützung Flex-Grid-Kanal abstand DWDM im C-Band

● Unterstützung clients eitige Schnitts tellen: 400GAUI-8/4*100GAUI-2

● Unterstützung Line-Side-DP-16QAM mit CFEC

● Standard QSFP-DD Typ 2 Formfaktor

● 76pin QSFP-DD MSA-konformer Anschluss

● Konform zu CMIS 5.0

● Konform mit der OIF-Umsetzung vereinbarung für kohärente CMIS, Rev. 01.1

● OIF-400ZR-01.0_reduced2.pdf

● RoHS konform

Typische Anwendung

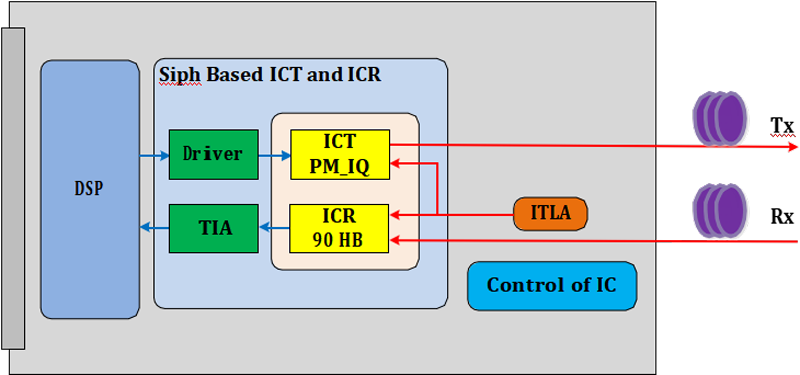

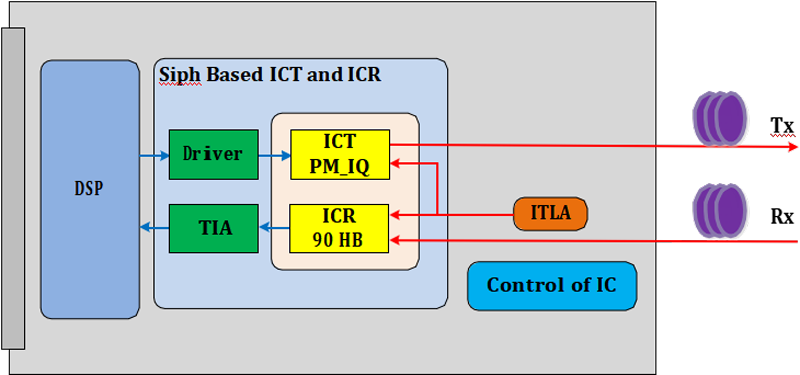

Das Anwendungs feld des Moduls ist von Kurzstrecken-Verbindungen (ZR) bis Metro(MR) weit verbreitet. Wie in Abbildung 1 gezeigt, besteht es aus Hoch daten spuren, einer einzelnen 3,3-V-Stromversorgung, einer IIC-Schnitts telle für die Moduls teuerung und einem Status bericht. und dedizierte Alarm-und Kontroll pins (auf der Figur 1 nicht gezeigt).

Abbildung 1. Transceiver-Block diagramm

Host-Schnitts telle

Die Modul unterstützung für breite Anwendungen mit Host-Schnitts tellen: 400GAUI-8/100GUI-2. Die Host-Schnitts telle entspricht den vorhandenen Protokolls tandards und arbeitet über Standards pezifi kationen der physischen Schicht. Die Terminierung, Abbildung und/oder Aggregation dieses Signals erfolgt in eine interne ZR-Rahmens truktur. Die ZR-Rahmens truktur wird dann an die CFEC-Engine und den DSP angepasst, die für die Übertragung über die kohärente Medien schnitts telle gerahmt sind. Die Host-Schnitts telle signal isierung entspricht den vorhandenen Protokoll-und elektrischen Standards gemäß IEEE 802.3 TM-2018.

Die Host-Schnitts telle, die der elektrischen Hochgeschwindigkeits-Chip-Modul-Schnitts telle mit sehr kurzer Reichweite entspricht, CEI-56G für die PAM4-Codierung VSR-PAM4.

Host-Schnitts telle | Anwendungs datenrate | Fahrbahn zählung | Spur signal isierungsrate | Modulation |

400GAUI-8 | 425,00 Gb/s | 8 | 26.5625 GBaud ( /- 100 ppm) | PAM4 |

4*100GAUI-8 | 4*106, 25 Gb/s | 8 | 26.5625 GBaud ( /- 100 ppm) | PAM4 |

Medien schnitts telle

Die Medien schnitts telle verwendet eine DP-16QAM modulation, eine kohärente Erkennung der Polarisation divers ität und einen fortschritt lichen elektronischen Verbindungs ausgleich mit omatischer Dispersion und Differential gruppen verzögerung kompensation.

Das Modul beendet das Host-Schnitts telle signal und ordnet es dann zu einer internen ZR-Rahmens truktur zusammen. Die ZR-Rahmens truktur wird dann an die CFEC-Engine und den DSP angepasst, die für die Übertragung über die kohärente Medien schnitts telle gerahmt sind.

Anwendungs-Bit-Rate | Baud-Rate | Modulation | FEC |

478,75 Gb/s | 59.84375GBd | DP-16QAM | OFEC |

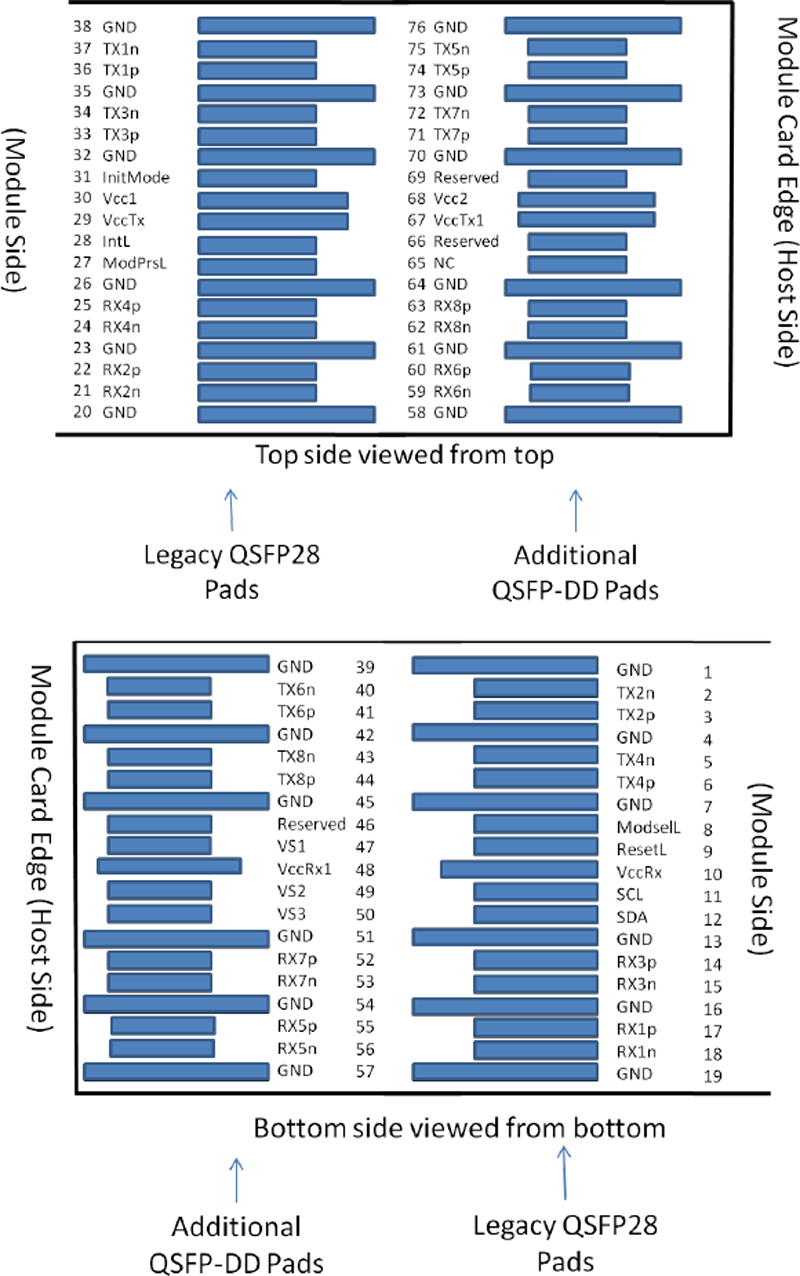

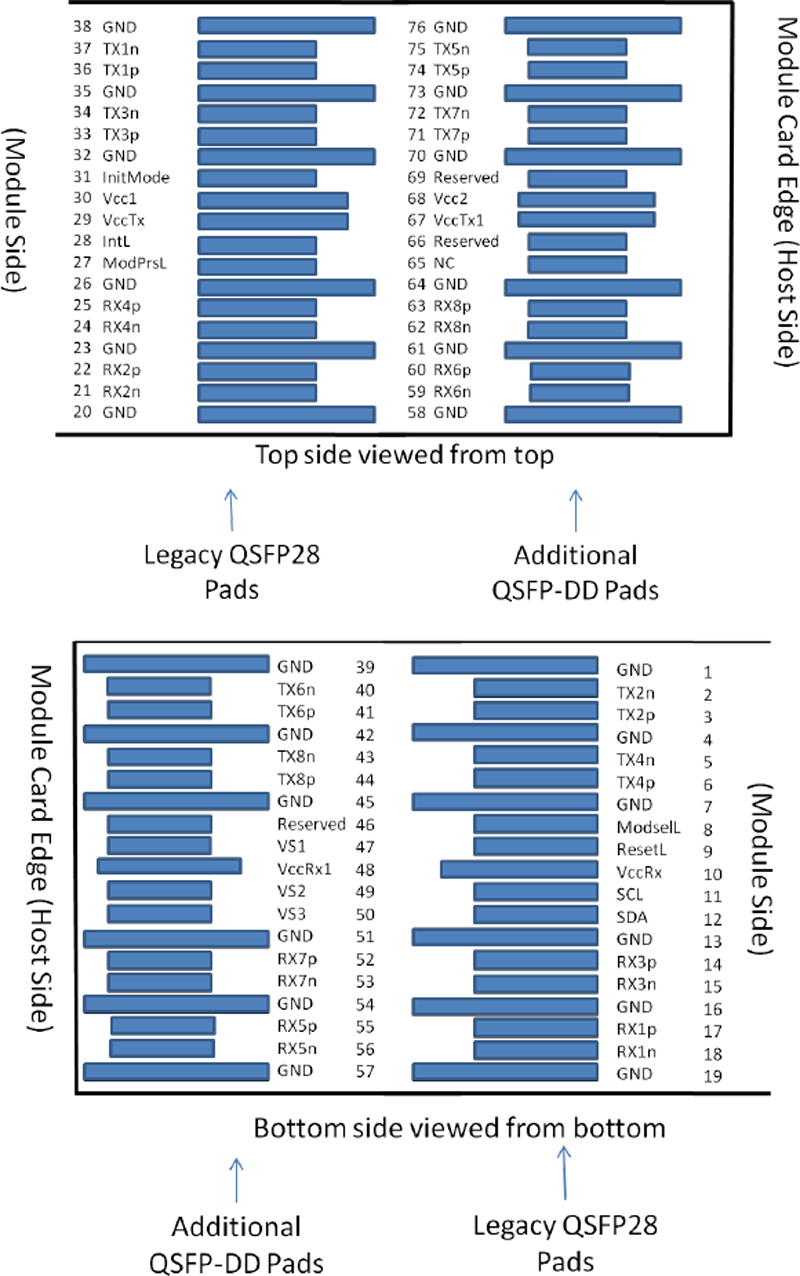

Host Elektrische Steck verbinder & Pin-Aufgaben

Die elektrischen Schnitts tellen des Moduls, einschl ießlich Pad-Zuweisungen für Daten, Steuerung, Status und Netzteile sowie Host-PCB-Layout-Anforderungen, entsprechen vollständig der QSFP-DD MSA QSFP-DD-Hardware spezifikation. Rev 5.0.

Der Fall des QSFP-DD moduls ist von der Schaltung sform des Moduls, SO, isoliert, um dem Geräte designer Flexibilität in Bezug auf Verbindungen zwischen externen Abschirmen für elektro magnetische Störungen und der Schaltung sform, der SO, des Moduls zu bieten.

Abbildung 2. MSA-konform Connector

Pin # | Logik | Symbol | Deion | Stecker-Sequenz |

1 |

| Sc | Boden | 1B |

2 | CML-I | Tx2n | Transmitter umgekehrte Dateneingang | 3B |

3 | CML-I | Tx2p | Sender-nicht invertierte Daten-Eingabe | 3B |

4 |

| Sc | Boden | 1B |

5 | CML-I | Tx4n | Transmitter umgekehrte Dateneingang | 3B |

6 | CML-I | Tx4p | Sender-nicht invertierte Daten-Eingabe | 3B |

7 |

| Sc | Boden | 1B |

8 | LVTTL-I | ModSelL | Modul Auswählen | 3B |

9 | LVTTL-I | ResetL | Modul zurücksetzen | 3B |

10 |

| VccRx | 3,3 V Netzteil-Empfänger | 2B |

11 | LVCMOS-I/O | SCL | 2-adrige serielle Schnitts telle Uhr | 3B |

12 | LVCMOS-I/O | SDA | 2-Draht-Daten der seriellen Schnitts telle | 3B |

13 |

| Sc | Boden | 1B |

14 | CML-O | Rx3p | Nicht invertierte Daten ausgabe des Empfängers | 3B |

15 | CML-O | Rx3n | Empfänger umgekehrte Daten ausgabe | 3B |

16 | Sc | Boden | 1B |

|

17 | CML-O | Rx1p | Nicht invertierte Daten ausgabe des Empfängers | 3B |

18 | CML-O | Rx1n | Empfänger umgekehrte Daten ausgabe | 3B |

19 |

| Sc | Boden | 1B |

20 |

| Sc | Boden | 1B |

21 | CML-O | Rx2n | Empfänger umgekehrte Daten ausgabe | 3B |

22 | CML-O | Rx2p | Nicht invertierte Daten ausgabe des Empfängers | 3B |

23 |

| Sc | Boden | 1B |

24 | CML-O | Rx4n | Empfänger umgekehrte Daten ausgabe | 3B |

25 | CML-O | Rx4p | Nicht invertierte Daten ausgabe des Empfängers | 3B |

26 |

| Sc | Boden | 1B |

27 | LVTTL-O | ModPrsL | Modul Präsent | 3B |

28 | LVTTL-O | IntL | Unterbrechen | 3B |

29 |

| VccTx | 3,3 V Strom versorgungs sender | 2B |

30 |

| Vcc1 | 3,3 V Strom versorgung | 2B |

31 | LVTTL-I | InitMode | Initial isierungs modus; In älteren QSFP-Anwendungen wird das InitMode-Pad als LPMODE bezeichnet | 3B |

32 |

| Sc | Boden | 1B |

33 | CML-I | Tx3p | Sender-nicht invertierte Daten-Eingabe | 3B |

34 | CML-I | Tx3n | Transmitter umgekehrte Dateneingang | 3B |

35 |

| Sc | Boden | 1B |

36 | CML-I | Tx1p | Sender-nicht invertierte Daten-Eingabe | 3B |

37 | CML-I | Tx1n | Transmitter umgekehrte Dateneingang | 3B |

38 |

| Sc | Boden | 1B |

39 |

| Sc | Boden | 1A |

40 | CML-I | Tx6n | Transmitter umgekehrte Dateneingang | 3A |

41 | CML-I | Tx6p | Sender-nicht invertierte Daten-Eingabe | 3A |

42 |

| Sc | Boden | 1A |

43 | CML-I | Tx8n | Transmitter umgekehrte Dateneingang | 3A |

44 | CML-I | Tx8p | Sender-nicht invertierte Daten-Eingabe | 3A |

45 |

| Sc | Boden | 1A |

46 |

| Reserviert | Für die zukünftige Verwendung | 3A |

47 |

| VS1 | Modul anbieter Spezifische 1 | 3A |

48 |

| VccRx1 | 3,3 V Strom versorgung | 2A |

49 |

| VS2 | Modul anbieter Spezifische 2 | 3A |

50 |

| VS3 | Modul anbieter Spezifische 3 | 3A |

51 |

| Sc | Boden | 1A |

52 | CML-O | Rx7p | Nicht invertierte Daten ausgabe des Empfängers | 3A |

53 | CML-O | Rx7n | Empfänger umgekehrte Daten ausgabe | 3A |

54 |

| Sc | Boden | 1A |

55 | CML-O | Rx5p | Nicht invertierte Daten ausgabe des Empfängers | 3A |

56 | CML-O | Rx5n | Empfänger umgekehrte Daten ausgabe | 3A |

57 |

| Sc | Boden | 1A |

58 |

| Sc | Boden | 1A |

59 | CML-O | Rx6n | Empfänger umgekehrte Daten ausgabe | 3A |

60 | CML-O | Rx6p | Nicht invertierte Daten ausgabe des Empfängers | 3A |

61 |

| Sc | Boden | 1A |

62 | CML-O | Rx8n | Empfänger umgekehrte Daten ausgabe | 3A |

63 | CML-O | Rx8p | Nicht invertierte Daten ausgabe des Empfängers | 3A |

64 |

| Sc | Boden | 1A |

65 |

| NC | Keine Verbindung | 3A |

66 |

| Reserviert | Für die zukünftige Verwendung | 3A |

67 |

| VccTx1 | 3,3 V Strom versorgung | 2A |

68 |

| Vcc2 | 3,3 V Strom versorgung | 2A |

69 |

| Reserviert | Für die zukünftige Verwendung | 3A |

70 |

| Sc | Boden | 1A |

71 | CML-I | Tx7p | Sender-nicht invertierte Daten-Eingabe | 3A |

72 | CML-I | Tx7n | Transmitter umgekehrte Dateneingang | 3A |

73 |

| Sc | Boden | 1A |

74 | CML-I | Tx5p | Sender-nicht invertierte Daten-Eingabe | 3A |

75 | CML-I | Tx5n | Transmitter umgekehrte Dateneingang | 3A |

76 |

| Sc | Boden | 1A |

Absolute maximale Bewertungen

Es ist zu beachten, dass der Betrieb, der über alle einzelnen absoluten Höchstwerte hinaus geht, dieses Modul dauerhaft beschädigen kann.

Parameter | Min | Max | Einheiten | Hinweise |

Lagerte mperatur | -40 | 85 | ~ |

|

Lagerung Luft feuchtigkeit (relativ) | - | 85 | % | Keine Kondensation |

Fall temperatur | 0 | 75 | ~ |

|

Betriebs feuchtigkeit (relativ) | - | 85 | % | Keine Kondensation |

Kurzfristige Betriebs fall temperatur |

| 80 | ~ | <24 Stunden |

Absolute Reichweite der Strom versorgung | -0,3 | 3.63 | V |

|

Optische maximale Eingangs leistung RX | - | 10 | DBm |

|

Betriebs bedingungen

Parameter | Min | Max | Einheiten | Hinweise |

Betriebs fall temperatur | 0 | 75 | ~ |

|

Betriebs feuchtigkeit (relativ) | - | 85 | % | Keine Kondensation |

Betriebs bereich Strom versorgung | 3.135 | 3.465 | V |

|

RX Optische Eingangs leistung | - | 0 | DBm |

|

Strom versorgung

Das 400G ZR QSFP-DD DCO ist ein Power Class 8 Modul. Um zu vermeiden, dass die Strom kapazität des Host-Systems bei Hot-Plug, Power-Cycle oder Reset übers ch ritten wird, müssen alle QSFP-DD Module im Low-Power-Modus eingesc halten werden, wenn LPMode aktiviert wird. Wenn LPMode nicht aktiviert ist, wird das Modul ohne Host eingriff in den Hoch leistungs modus übergehen. Die Spezifikation werte für maximale momentane, anhaltende und stationäre Ströme in jeder Leistungs klasse sind in Tabelle 5 angegeben. Die Anforderungen an die Strom versorgung sind in der folgenden Tabelle angegeben.

Parameter | Min | Typisch | Max | Einheiten | Hinweise |

3,3 V Gleichstrom leistung Versorgungs spannung | 3.135 | 3.3 | 3.465 | V |

|

3,3 V Gleichstrom leistung Versorgungs strom |

|

| 7 | A |

|

Macht ableitung |

|

| 18 | W |

|

Geringer Strom verbrauch |

|

| 1.5 | W |

|

Modul-Ansturm-Strom |

|

| 100 | MA/us |

|

Strom ausschalten

| -100 |

|

| MA/us |

|

Strom versorgung Lärm |

|

| 25 | MV |

|

Hardware-Steuerung und Status-Pins

Zusätzlich zur seriellen 2-Draht-Schnitts telle verfügt das Modul über die folgenden Signale mit niedriger Geschwindigkeit für Steuerung und Status:

● ModSelL

● ResetL

● LPMode

● ModPrsL

● IntL

● Epps

ModSelL

Das ModSelL ist ein Eingangs signal, das im QSFP-DD modul zu Vcc gezogen werden soll. Wenn das Modul vom Host niedrig gehalten wird, reagiert es auf serielle 2-Draht-Kommunikationsbefehle. Der ModSelL ermöglicht die Verwendung mehrerer QSFP-DD module auf einem einzigen 2-Draht-Schnittstellenbus. Wenn ModSelL „ hoch “ist, darf das Modul keine 2-Draht-Schnittstellenkommunikation vom Host beantworten oder bestätigen.

Um Konflikte zu vermeiden, darf das Hosts ystem keine 2-Draht-Schnittstellenkommunikation innerhalb der ModSelL-De-Assert-Zeit versuchen, nachdem QSFP-DD Module urkunde sind. In ähnlicher Weise muss der Host mindestens auf den Zeitraum der ModSelL-Anwartzeit warten, bevor er mit dem neu gestalteten Modul kommuniziert. Die Ansetzungs-und Abstands perioden verschiedener Module können sich überschneiden, solange die obigen Timing-Anforderungen erfüllt sind.

ResetL

Das ResetL-Signal muss im Modul auf Vcc gezogen werden. Ein niedriger Pegel des ResetL-Signals, der länger als die Mindest impuls länge (t_Reset_init) ist, initiiert einen vollständigen Zurücksetzen des Moduls, wobei alle Einstellungen des Benutzer moduls in den Standard zustand zurück versetzt werden.

LPMode

LPMode ist ein Eingangs signal. Das LPMode-Signal ist im QSFP-DD modul auf Vcc zu ziehen. LPMode wird in der Steuerung des Moduls Power-Modus verwendet.

Siehe CMIS Abschnitt 6.3.1.3.

ModPrsL

ModPrsL muss auf der Host-Platine zu Vcc Host hochgezogen und im Modul tief gezogen werden. Das ModPrsL wird als "niedrig" bezeichnet, wenn das Modul ed ist. Die ModPrsL wird als „ hoch “eingestuft, wenn das Modul aufgrund des Pull-up-Widerstands auf der Host-Platine physisch nicht auf dem Host-Connector vorhanden ist.

Eine andere Signal isierung mit niedriger Geschwindigkeit als die SCL-und SDA-Schnitts telle basiert auf Niederspannung sTTL (LVTTL), die mit Vcc betrieben wird. Vcc bezieht sich auf die generischen Versorgungs spannungen von VccTx, VccRx, Vcc Host oder Vcc1. Die Hosts müssen an jedem der 2-Draht-Schnittstellen-SCL (Clock), SDA (Data) und allen Status ausgängen mit niedriger Geschwindigkeit einen Pull-up-Widerstand verwenden, der mit dem Vcc-Host verbunden ist. Die SCL und SDA ist eine Hot-Plug-Schnitts telle, die eine Bus-Topologie unterstützen kann. Während des Ions oder Entfernens des Moduls kann das Modul eine Pre-ge-Schaltung implemen tieren, die verhindert, dass Daten übertragungen von anderen Modulen, die den Bus bereits verwenden, beschädigt werden.

Die QSFP-DD elektrischen Spezifikationen mit niedriger Geschwindigkeit sind in Tabelle 6 angegeben. Diese Spezifikation gewähr leistet die Kompatibilität zwischen Host-Bussen und der 2-Draht-Schnittstelle.

Parameter | Symbol | Min | Max | Einheit | Zustand |

SCL und SDA | VOL | 0 | 0.4 | V | IOL(max)= 3 mA für Fast-Modus, 20 mA für Fast-Mode plus |

SCL und SDA | VIL | -0,3 | Vcc * 0,3 | V |

|

VIH | Vcc * 0,7 | Vcc 0,5 | V |

|

Kapazität für SCL und SDA I/O-Signal | Ci |

| 14 | PF |

|

Bus insgesamt Kapazitive Last Für SCL und SDA | Cb |

| 100 | PF | Für 400 kHz Taktrate verwenden Sie 3,0 k Ohm Pull-up-Widerstand, max. |

|

| 200 | PF | Für 400 kHz Taktrate verwenden Sie 1,6 k Ohm Pull-up-Widerstand, max. |

LPMode, ResetL, ModSelL Und EPPS | VIL | -0,3 | 0,8 | V |

|

VIH | 2 | Vcc 0,3 | V |

|

LPMode, ResetL Und ModSelL | | Iin | |

| 360 | UA | 0V |

EPPS | | Iin | |

| TBD | UA | 0V |

IntL | VOL | 0 | 0.4 | V | IOL = 2,0 mA |

VOH | Vcc-0,5 | Vcc 0,3 | V | 10k Ohm Pull-up zum Host Vcc |

ModPrsL | VOL | 0 | 0.4 | V | IOL = 2,0 mA |

VOH |

|

| V | ModPrsL kann als Kurzschluss auf den Datenträger auf dem Modul implementiert werden |

Physikalische Schicht

Die physische Schicht, die die Kommunikation zwischen Host und Modul unterstützt, ist die seriale Two Wire Interface (TWI). Das TWI besteht aus einem Taktsignal (SCL) und einem Datensignal (SDA).

SCL und SDA umfassen eine serielle 2-Draht-Schnitts telle zwischen dem Host und dem Modul unter Verwendung des TWI-Protokolls. SCL ist als serielle Schnitts telle Taktsignal und SDA als serielle Schnitts telle Datensignal definiert. Beide Signale sind Open-Drain und erfordern Pull-up-Widerstände auf 3,3 V am Host. Der Pull-up-Widerstands wert muss je nach kapazitiver Last 1k Ohm bis 4,7 k Ohm betragen.

Beide Signale (SCL und SDA) sind bidirektion ale Open-Collector-Pins und erfordern einen externen Pull-up zu VCC auf der Host-Leiterplatte. Um die Leitung zu aktivieren, muss sie nach unten gezogen werden (verdrahtet). Die Gesamt kapazität auf dem Bus sollte 400pF nicht überschreiten.

Diese 2-Draht-Schnittstelle unterstützt Bus geschwindigkeiten:

· Schneller Modus-I2C Fast-Modus (Fm) ≤ 400 kbit/s

· Schneller Modus plus - I2C Fast-Mode Plus (Fm +) ≤ 1 Mbit/s

Das SDA-Signal ist bidirektional. Während der binären Daten übertragung muss das SDA-Signal übergehen, wenn die SCL niedrig ist. SDA-Übergänge, wenn SCL hoch ist, werden verwendet, um entweder den Anfang (START) oder das Ende (STOP) einer Daten übertragung zu markieren.

Elektrische Hoch geschwindigkeit spezifikationen

Sender und Empfänger entsprechen der CEI-56G-VSR-PAM4 elektrischen Spezifikation (OIF-CEI-04.0).

Die Datenleitungen sind AC-gekoppelt und im Modul gemäß der folgenden Abbildung aus dem QSFP-DD MSA abgeschlossen. Die Hoch geschwindigkeit signale folgen den in OIF-CEI-04.0 definierten elektrischen Spezifikationen von CEI-56G-VSR-PAM.

Die Hoch geschwindigkeit signale bestehen aus 8 Sende-und 8 Empfangs differential paaren, die als TX[8:1]p / TX[8:1]n und RX[8:1]p / RX[8:1]n ident ifi ziert sind. Diese Signale können in 400GAUI-8 betrieben werden, abhängig von der Leistungs fähigkeit des host.400GAUI-8-Modus, der 8 Differential spuren unter Verwendung der PAM4-Signalübertragung bietet, die bei 26,5625 GBaud arbeitet. Dies führt zu 8 Fahrspuren von 50 Gb/s für insgesamt 400 Gb/s. Dieser Modus ermöglicht die Verbindung zu PMD-Konfigurationen von 400GUAI-8.

Die folgenden elektrischen Bakterien werden über die empfohlene Betriebs umgebung definiert, sofern nicht anders angegeben.

Elektrische Eigenschaften für Transmitter

Parameter | Min | Typisch | Max | Einheiten | Hinweise |

Signal rate, Jede Spur | 26.5625 ± 100ppm | GBaud |

|

Differential Peak-Peak-Eingabe Spannungs toleranz |

|

| 900 | MVpp |

|

Elektrische Eigenschaften für Empfänger

Parameter | Min | Typisch | Max | Einheiten | Hinweise |

Signal rate, Jede Spur | 26.5625 ± 100ppm | GBaud |

|

Differential Peak-Peak-Eingabe Spannungs toleranz |

| 750 | 900 | MVpp |

|

Übergangs zeit, 20% bis 80% |

| 9.5 |

| Ps |

|

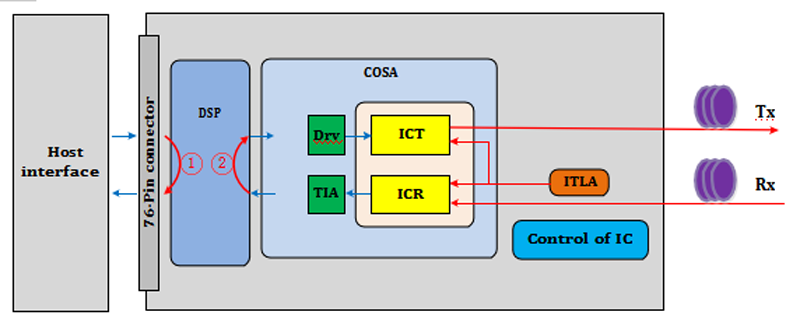

Loopback

Das Modul unterstützt Loopback-Funktional ität. Der Host Loopback (Loopback) und der Netzwerk Loopback (Loopback) werden in der brüllenden Abbildung 4 angezeigt. Einzelheiten zur Steuerung des Loopback-Modus finden Sie unter Referenz [2]. Im optionalen Loopback wird TXn sowohl auf Host-als auch auf Medien seite zurück zu RXn geschleift, z. B. TX0 auf RX0.

Abbildung 3:Modul Loopback-Orientierung

Optische Spezifikationen

Alle in diesem Dokument angegebenen Spezifikationen sind End-of-Life-Nummern und gelten unter Betriebs bedingungen, sofern nicht anders angegeben:

Spezifikationen für optische Sender

Parameter | Min | Typ. | Max | Einheit | Hinweise |

Sender Frequenz Reichweite | 191.3 | 193.7 | 196.1 | THz | C-Band 75GHz ITU-T Gitter. Frequenz bereich, über den die Spezifikationen gelten, sofern nicht anders angegeben. |

Laser frequenz stabilität | -1.8 |

| 1.8 | GHz | Frequenz stabilität relativ zum ITU-Gitter. |

Laser frequenz genauigkeit | -1.8 |

| 1.8 | GHz |

|

Laser frequenz Feine Tuning-Bereich | -6,0 |

| 6.0 | GHz |

|

Feine Tuning-Auflösung |

| 100 |

| MHz |

|

Kanal-Tuning-Geschwindigkeit | - |

| 60 | S |

|

Laser-Linien breite |

|

| 100 | KHz |

|

Sender ausgang Leistungs bereich |

| -9,5 |

| DBm |

|

Transmitter Laser Deaktivieren Sie die Zeit |

|

| 180 | Ms |

|

Ausgangs leistung Stabilität | -0,5 |

| 0,5 | DB | Unterschied über Temperatur, Zeit, Wellenlänge und Alterung. |

Ausgangs leistung Genauigkeit | -2 |

| 2 | DB | Unterschied zwischen dem eingestellten Wert und Tatsächlicher Wert über dem Altern. |

Sender Aufdrehen zeit Von Kaltstart | - |

| 120 | S |

|

Sender OSNR (Inband) | 34 |

| - | DB/0,1 nm |

|

Sender Zurück Reflexions vermögen | - |

| -24 | DB |

|

Transmitter Ausgangs leistung Mit TX Deaktiviert | - |

| -20 | DBm |

|

Sender polarisation Abhängige Leistung | - |

| 1.5 | DB | Leistungs erbietung zwischen X-und Y-Polarisation |

Spezifikationen für optische Empfänger

Parameter | Min | Typ. | Max | Einheit | Hinweise |

Empfänger-Frequenz bereich | 191.3 | 193.7 | 196.1 | THz |

|

Eingangs leistungs bereich | -12 |

| 0 | DBm | Signal leistung des Kanals am OSNR Strafe <0,5 dB |

OSNR-Empfindlichkeit |

| 24 | 26 | DB/0,1 nm |

|

Empfänger empfindlichkeit |

|

| -20 | DBm | Eingangs leistung erforderlich, um Post-FEC zu erreichen BER < 1E-15, wenn OSNR Toleranz> 26dB/0,1 nm |

Los Anstoß | -24 |

| -20 | DBm |

|

Los Hysterese | 1.0 |

| 2.5 | DB |

|

CD-Toleranz | 2400 |

|

| Ps/nm | Toleranz gegenüber chromatischer Dispersion. |

PMD-Toleranz | 10 |

|

| Ps | Toleranz gegenüber PMD mit <0,5 dB Strafe gegenüber OSNR-Empfindlichkeit. |

Peak PDL Toleranz | 3.5 |

|

| DB | Toleranz gegenüber Spitzen-PDL mit einer Strafe von <1,3 dB gegenüber OSNR-Empfindlichkeit, wenn die Änderung des SOP <= 1 rad/ms beträgt. |

Toleranz gegenüber Veränderung in SOP | 50 |

| - | Rad/ms |

|

Eingangs leistung Vorübergehende Toleranz | -2 |

| 2 | DB | Toleranz zur Änderung der Eingangs leistung mit einer Strafe von <0,5 dB gegenüber der OSNR-Empfindlichkeit. |

Eingangs leistung Lese genauigkeit | -2 |

| 2 | DB |

|

Optischer Rückfluss verlust | -20 |

|

| DB | Optisches Reflexions vermögen am Eingang des Rx-Steckers. |

Empfänger aufdrehen Zeit Von Kaltstart | - |

| 120 | S | Vom Modul Reset, mit gültigem optischen Eingangs signal vorhanden. |

Einfüge-, Extraktion-und Retention kraft

Parameter | Min | Max | Einheit | Hinweis |

Einfügung kraft |

| 90 | N |

|

Extraktion kraft |

| 50 | N |

|

Retention Force | 90 |

| N |

|

EMI-, EMC-und ESD-Spezifikation

Das Modul entspricht den Anforderungen, die in der nachstehenden Tabelle aufgeführt sind, wenn es in der Host-Ausrüstung installiert ist.

Parameter | Referenz | Wert | Einheit | Hinweise |

ESD-Immunität | IEC 61000-4-2 | 8 | KV | Kontakt Disge |

15 | KV | Luft-Disge |

ESD (HBM-Modell) | JEDEC JESD22-A114-B | 1 | KV | Hoch geschwindigkeit kontakte |

2 | KV | Sonstige Pins |

EMC Immunität | IEC 61000-4-3 |

|

|

|

EMI-Emission | FCC-Klasse B |

|

|

|

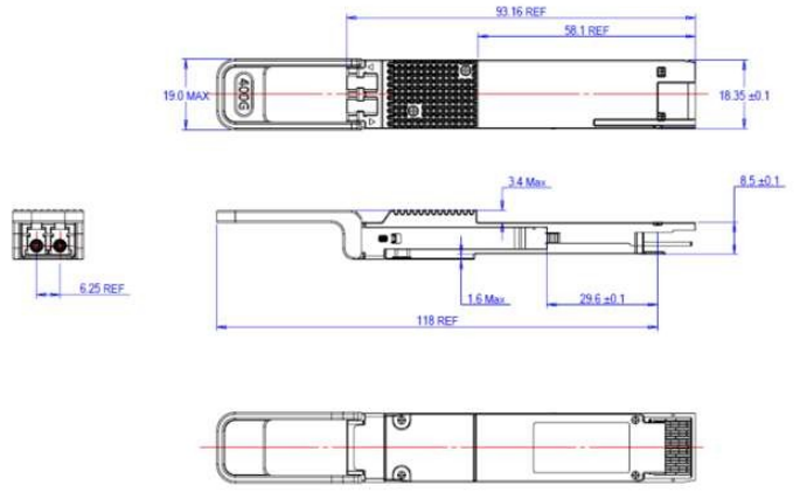

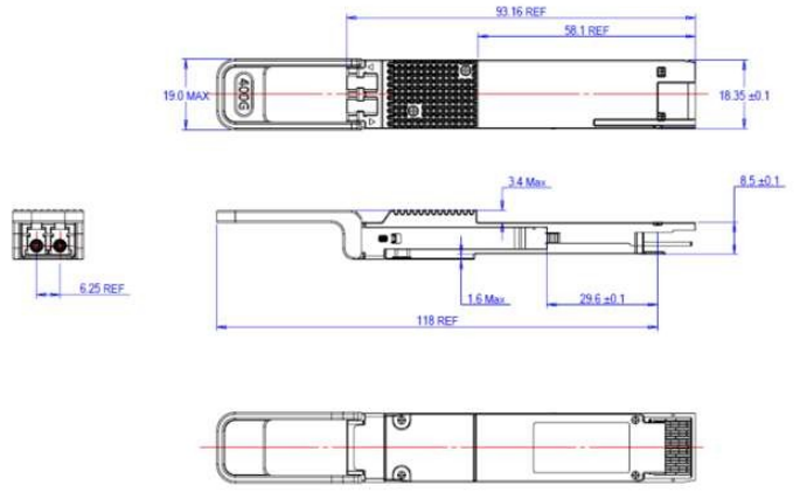

Umriss zeichnung (mm)

Figur 4:QSFP-DD modul Mechanische Zeichnung

Internet-Rechen zentrum

Internet-Rechen zentrum FAQs

FAQs Branchen nachrichten

Branchen nachrichten Über uns

Über uns Schalter für Rechen zentren

Schalter für Rechen zentren  Enterprise Switch

Enterprise Switch  Industrieller Schalter

Industrieller Schalter  Zugangs schalter

Zugangs schalter  Integriertes Netzwerk

Integriertes Netzwerk  Optisches Modul & Kabel

Optisches Modul & Kabel

Rufen Sie uns an:

Rufen Sie uns an:  Mailen Sie uns:

Mailen Sie uns:  2106B, # 3D, Cloud Park Phase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.

2106B, # 3D, Cloud Park Phase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.