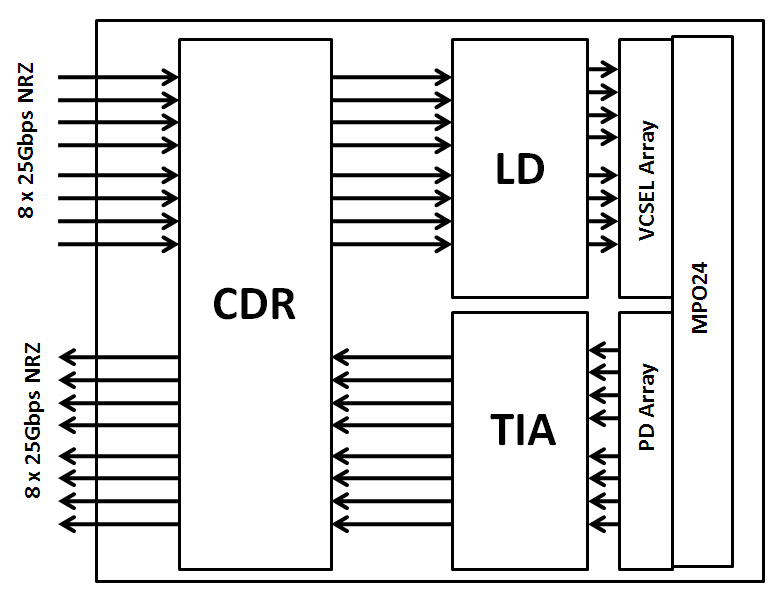

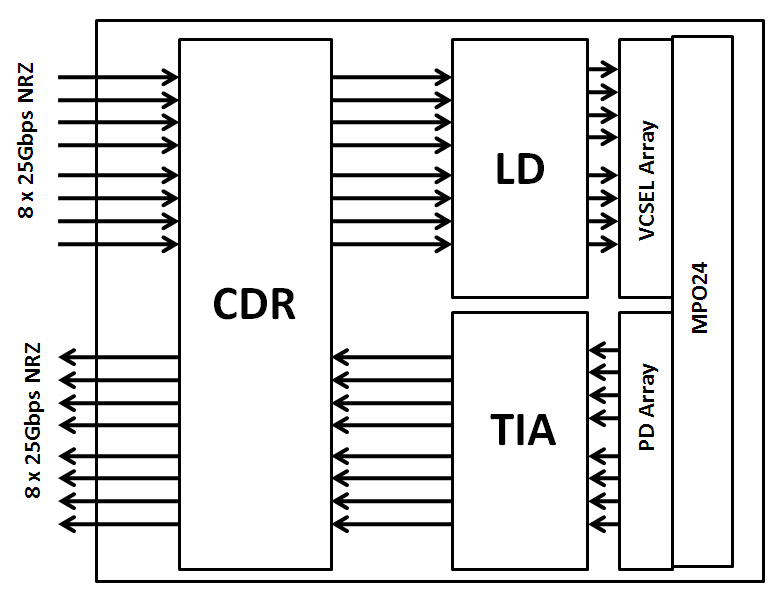

2x100GBASE-SR4 QSFPDD-Transceiver ist eine Art von parallelem Transceiver, VCSEL und PIN-Array-Paket ist die Schlüssel technik, über I2C-System kann Kontakt mit Modul. Es ist eine acht kanal ige, steck bare, parallele, faser optische QSFP-Doppel dichte für 2x100 Gigabit-Ethernet-Anwendungen. Hoch leistungs modul für mehrspurige Daten kommunikations-und Verbindungs anwendungen mit kurzer Reichweite. Es integriert acht Daten spuren in jede Richtung mit einer Bandbreite von 8x25,78125 Gbps. Jede Spur kann mit 25,78125 Gbps bis zu 70 m mit OM3-Faser oder 100 m mit OM4-Faser betrieben werden. Diese Module sind für den Betrieb über Multimode-Faser systemen mit einer nominalen Wellenlänge von 850nm ausgelegt. Die elektrische Schnitts telle verwendet einen Steck verbinder vom Typ 76 Kontakt kanten. Die optische Schnitts telle verwendet einen 24 Faser MTP (MPO) Stecker. Dieses Modul enthält eine bewährte Schaltung und VCSEL-Technologie, um eine zuverlässige lange Lebensdauer, hohe Leistung und einen konsistenten Service zu bieten.

Abbildung 1. Modul Block diagramm

Merkmale

● 8 Kanäle Vollduplex-Transceiver-Module

● Übertragungs datenrate bis zu 26Gbps pro Kanal

● 8 Kanäle 850nm VCSEL-Array

● 8 Kanäle PIN Foto detektor Array

● Interne CDR-Schaltungen auf Empfänger-und Sender kanälen

● Unterstützung CDR-Bypass

● Geringer Strom verbrauch <4W

● Heißer steck barer QSFP DD-Formfaktor

● Maximale Verbindungs länge von 70m auf OM3 Multimode-Faser (MMF) und 100m auf OM4 MMF

● MPO24-Steckdose

● Betriebs fall temperatur 0 °C bis 70 °C

● 3,3 V Versorgungs spannung

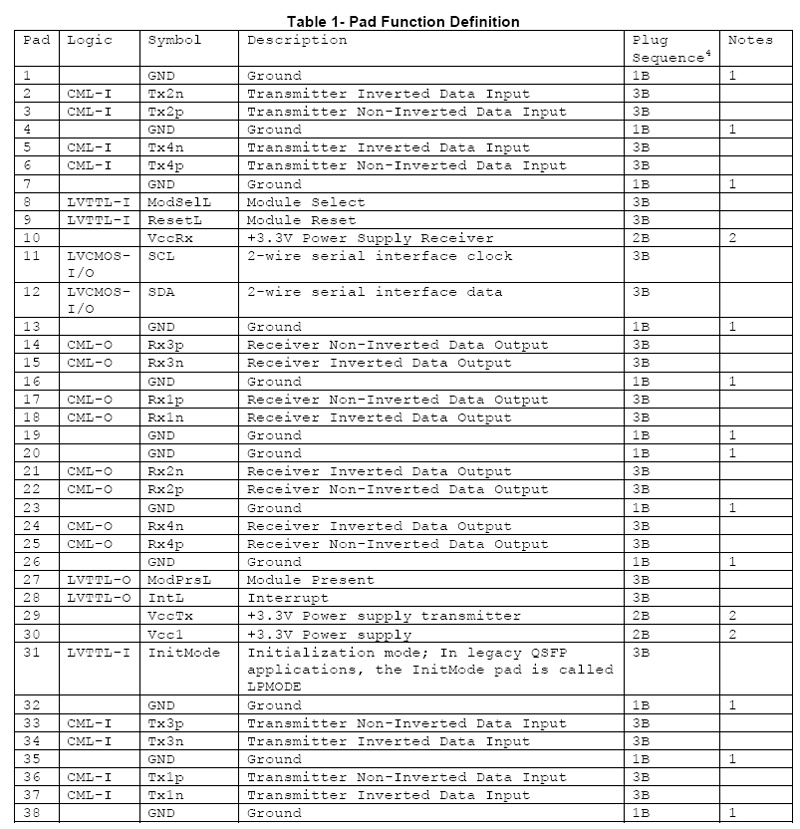

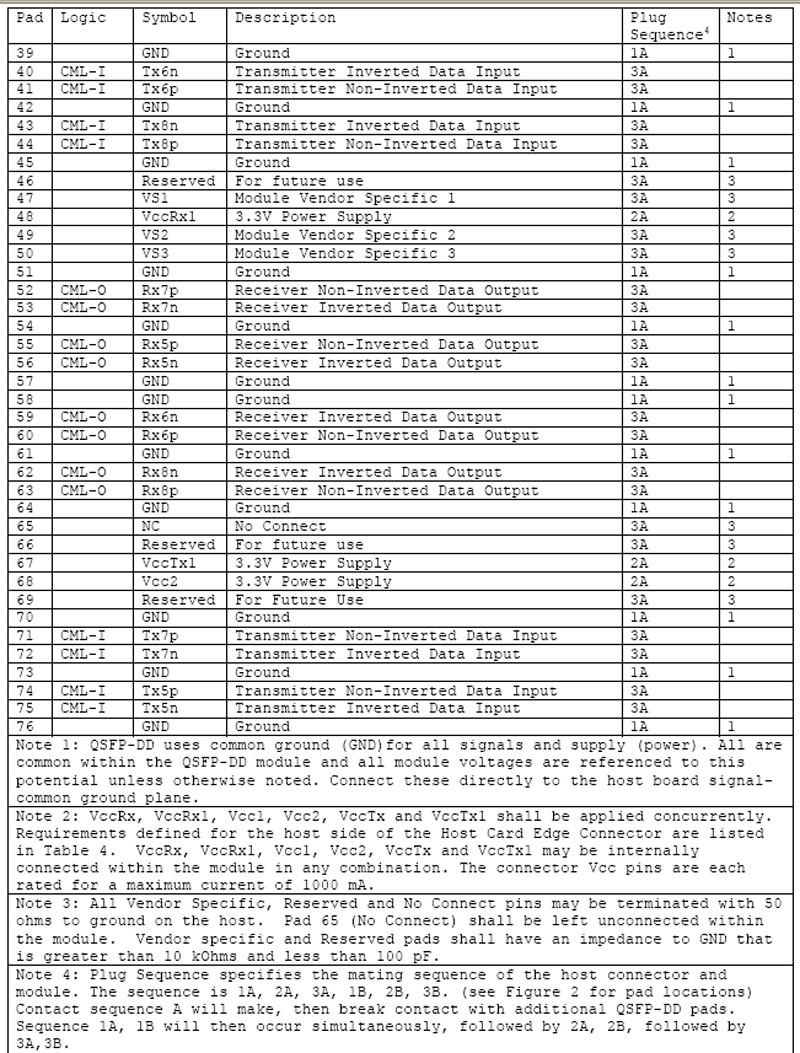

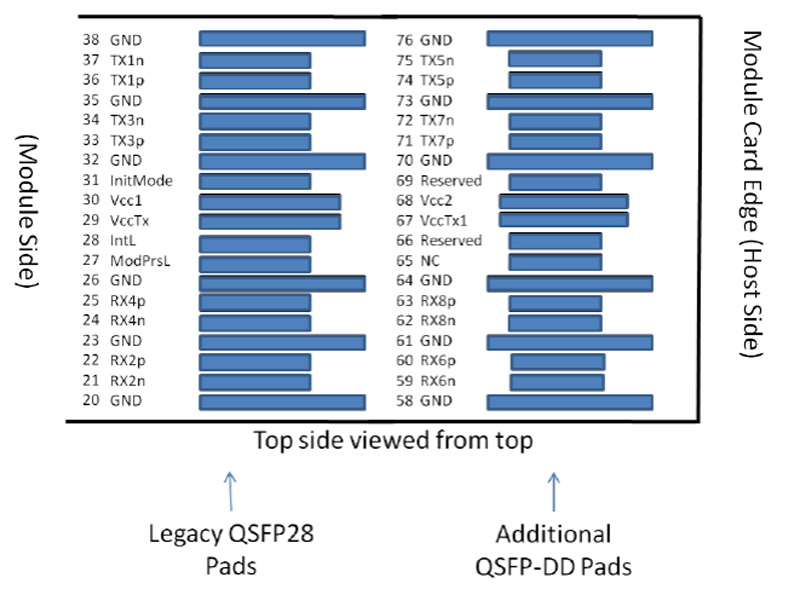

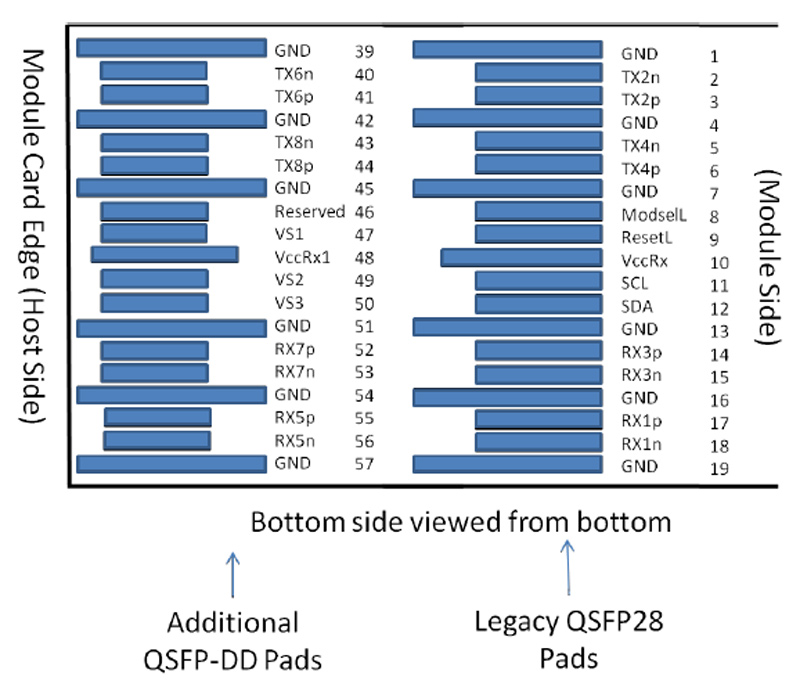

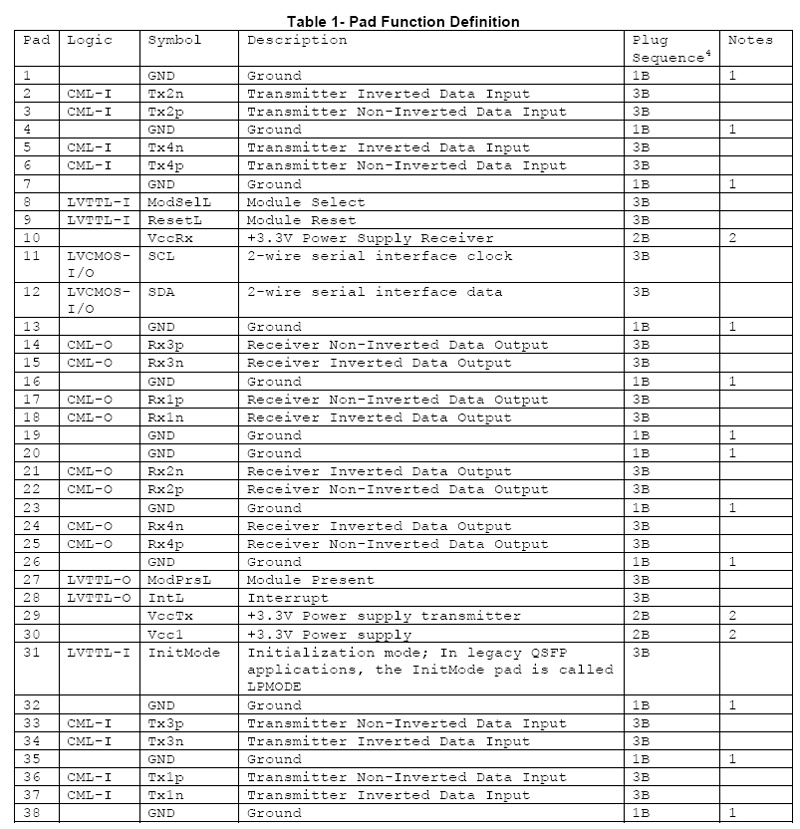

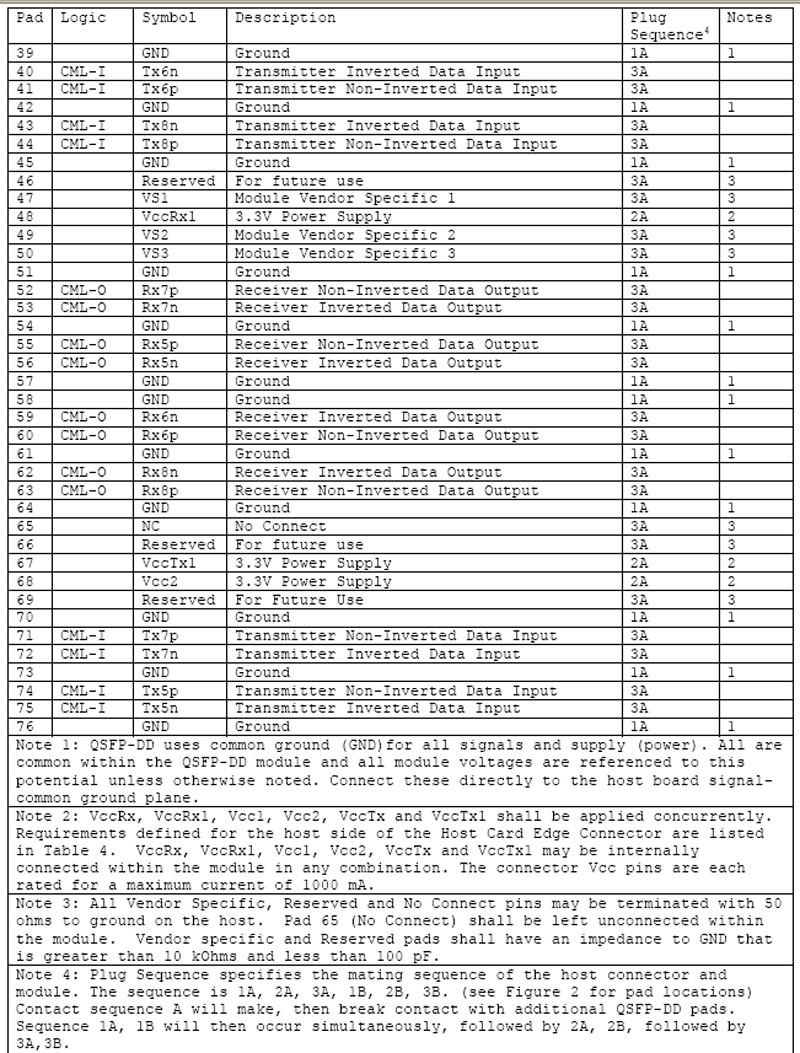

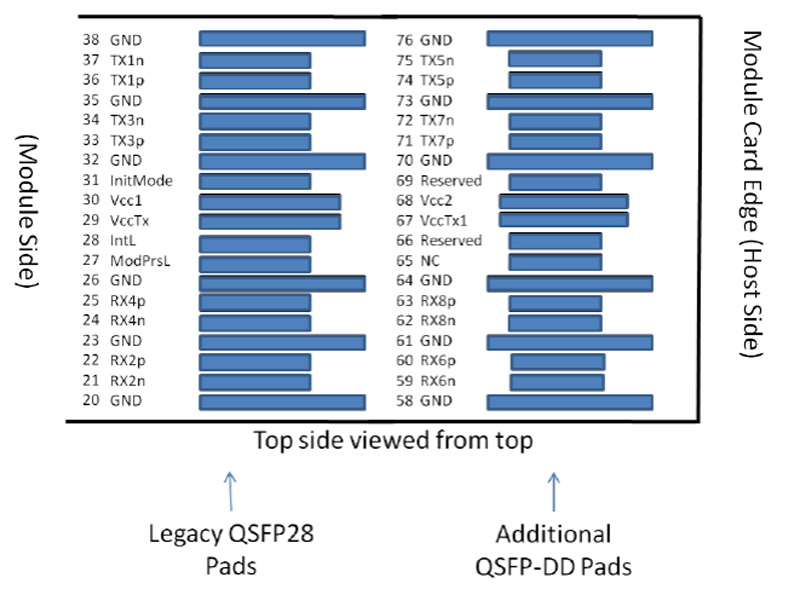

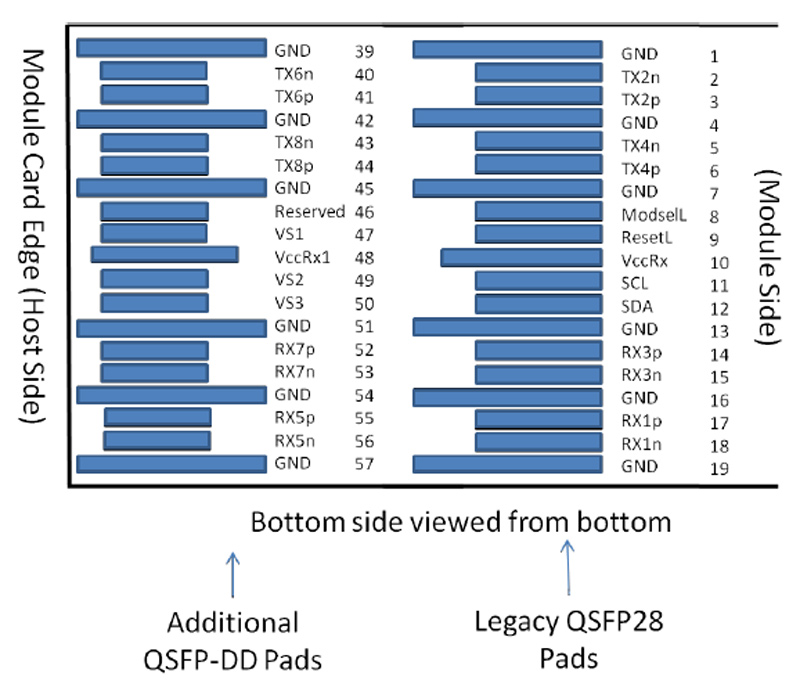

Pin Deion

Abbildung 2. Elektrische Pin-Out-Details

ModSelL Pin

Das ModSelL ist ein Eingangs signal, das im QSFP-DD modul zu Vcc gezogen werden muss. Wenn das Modul vom Host niedrig gehalten wird, reagiert es auf serielle 2-Draht-Kommunikationsbefehle. Der ModSelL ermöglicht die Verwendung mehrerer QSFP-DD module auf einem einzigen 2-Draht-Schnittstellenbus. Wenn ModSelL „ hoch “ist, darf das Modul keine 2-Draht-Schnittstellenkommunikation vom Host beantworten oder bestätigen.

Um Konflikte zu vermeiden, darf das Hosts ystem keine 2-Draht-Schnittstellenkommunikation innerhalb der ModSelL-De-Assert-Zeit versuchen, nachdem QSFP-DD Module urkunde sind. In ähnlicher Weise muss der Host mindestens auf den Zeitraum der ModSelL-Anwartzeit warten, bevor er mit dem neu gestalteten Modul kommuniziert. Die Ansetzungs-und Abstands perioden verschiedener Module können sich überschneiden, solange die obigen Timing-Anforderungen erfüllt sind.

ResetL Pin

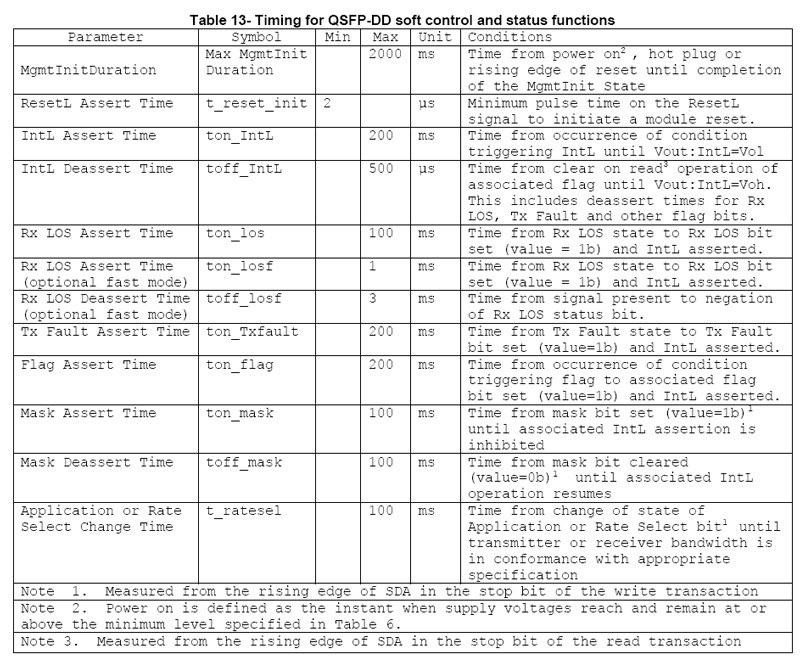

Das ResetL-Signal muss im Modul auf Vcc gezogen werden. Ein niedriger Pegel des ResetL-Signals, der länger als die Mindest impuls länge (t_Reset_init) ist (siehe Tabelle 13), löst einen vollständigen Modul reset aus und kehrt alle Benutzer module in ihren Standard zustand zurück.

InitMode Pin

InitMode ist ein Eingangs signal. Das InitMode-Signal muss im QSFP-DD modul auf Vcc hochgezogen werden. Mit dem InitMode-Signal kann der Host definieren, ob das QSFP-DD modul unter der Steuerung der Host-Software (InitMode behauptet High) oder der Modul hardware steuerung (InitMode deasered Low) initial isiert wird. Unter der Steuerung der Host-Software muss das Modul im Low-Power-Modus bleiben, bis die Software den Übergang zum High-Power-Modus gemäß Abschnitt 7.5 ermöglicht. Unter Hardware-Kontrolle (InitMode de-ased Low) kann das Modul sofort in den High Power-Modus übergehen, nachdem die Verwaltungs schnitts telle initial isiert wurde. Der Host darf den Zustand dieses Signals nicht ändern, während das Modul vorhanden ist. In älteren QSFP-Anwendungen wird dieses Signal LPMode genannt. Siehe SFF-8679 für Signal deion.

ModPrsL Pin

ModPrsL muss auf der Host-Platine zu Vcc Host hochgezogen und im Modul geerdet werden. Das ModPrsL wird als "niedrig" bezeichnet, wenn das Modul ed und "High" desuperiert wird, wenn das Modul physisch im Host-Connector fehlt.

IntL Pin

IntL ist ein Ausgangs signal. Das IntL-Signal ist ein Open-Collector-Ausgang und muss auf der Host-Platine an Vcc Host gezogen werden. Wenn das IntL-Signal niedrig angegeben wird, zeigt es eine Änderung des Modul zustands, einen möglichen Modul betriebs fehler oder einen für das Hosts ystem kritischen Status an. Der Host ident ifi ziert die Quelle des Interrupts mithilfe der seriellen 2-Draht-Schnittstelle. Das IntL-Signal wird als „ Hoch “eingestuft, nachdem alle eingestellten Interrupt-Flags gelesen wurden.

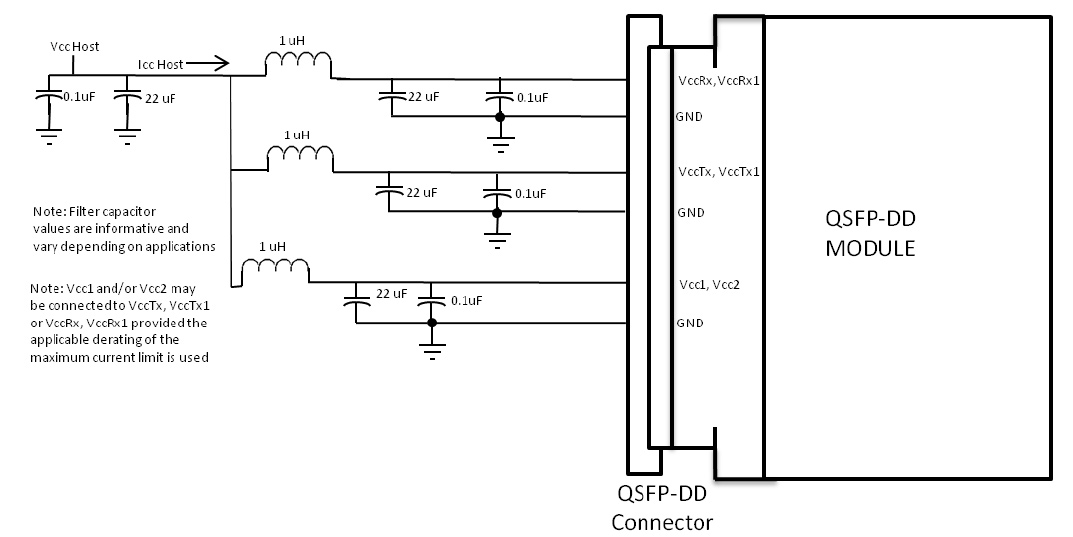

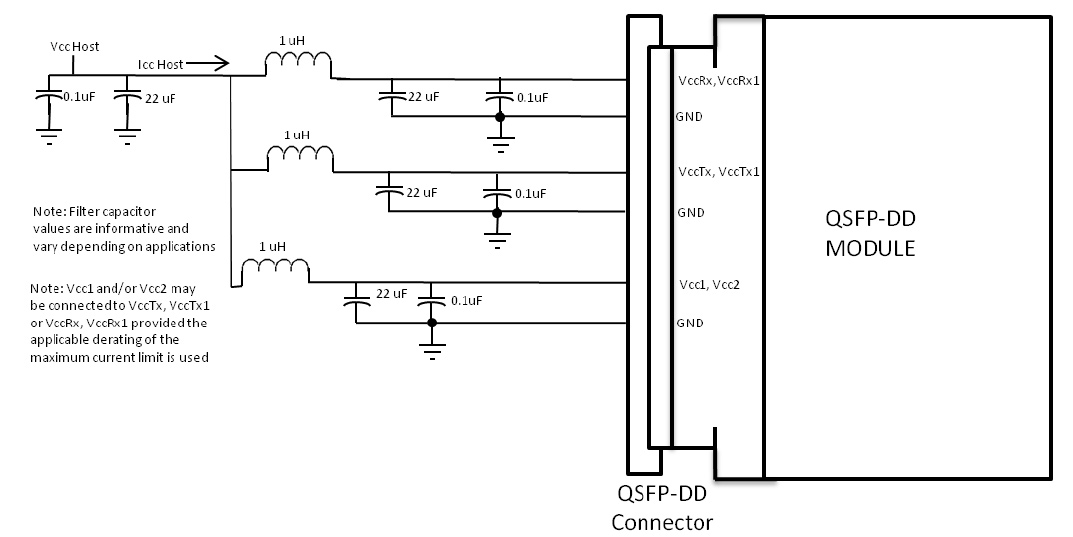

Strom versorgungs filterung

Die Host-Platine sollte die in Figure3 gezeigte Strom versorgungs filterung verwenden.

Abbildung 3. Host Board Netzteil Filterung

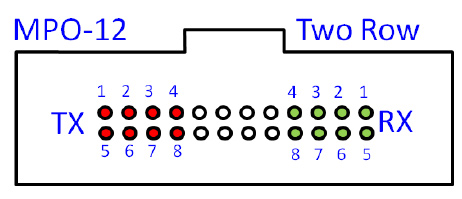

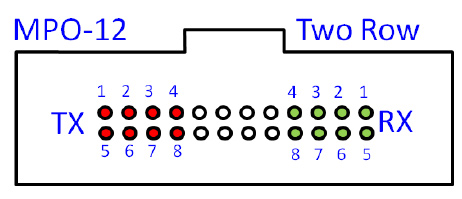

Optische Schnitts telle spuren und Zuweisung

Der optische Schnitts telle anschluss ist ein männlicher MPO24-Stecker.

Abbildung 4. Optischer Behälter und Kanal orientierung

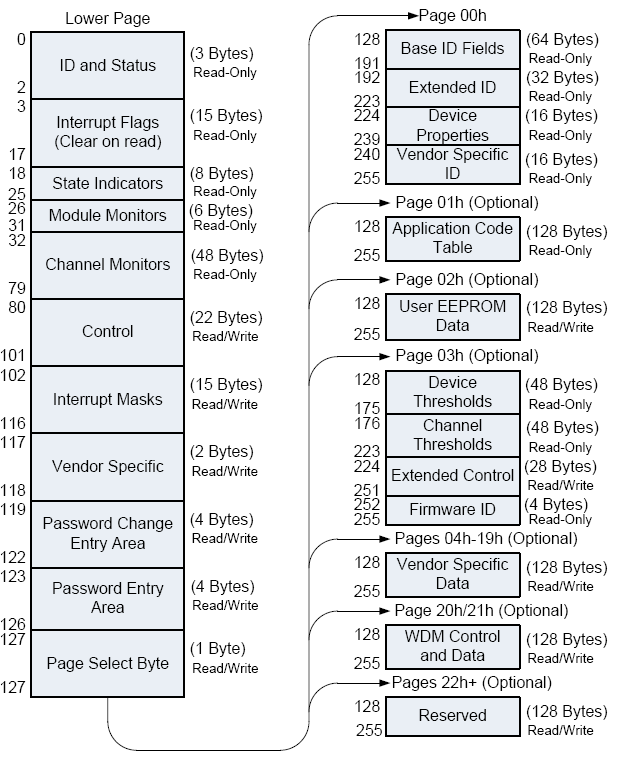

DIAGNOSTISCHE ÜBERWACHUNGS SCHNITTS TELLE (OPTIONAL)

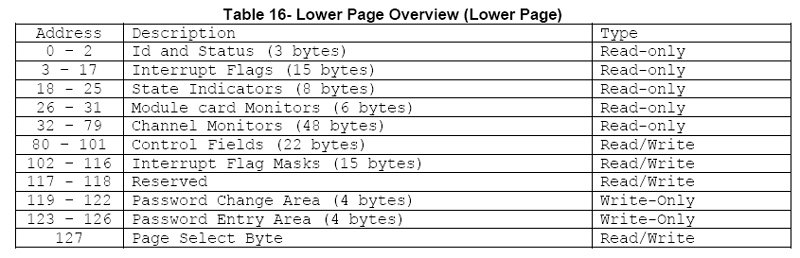

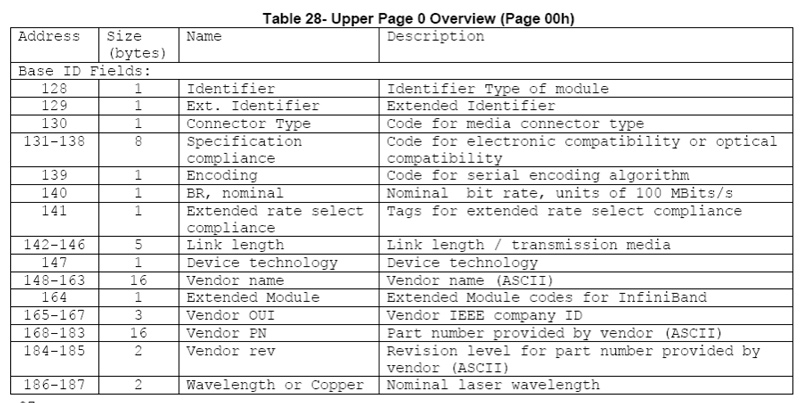

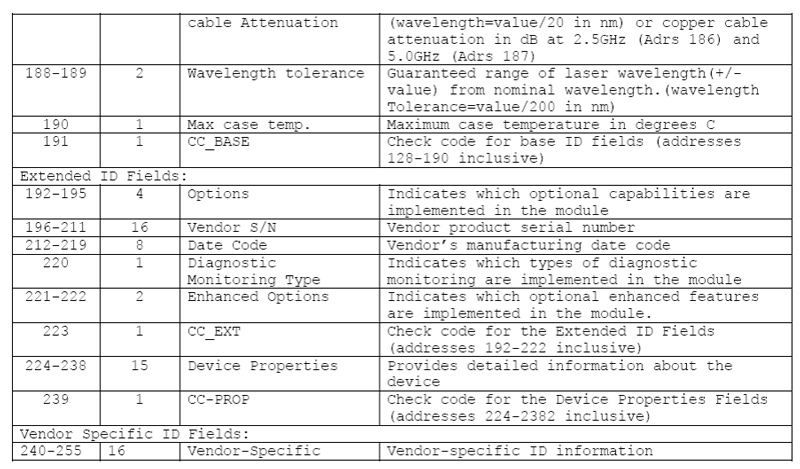

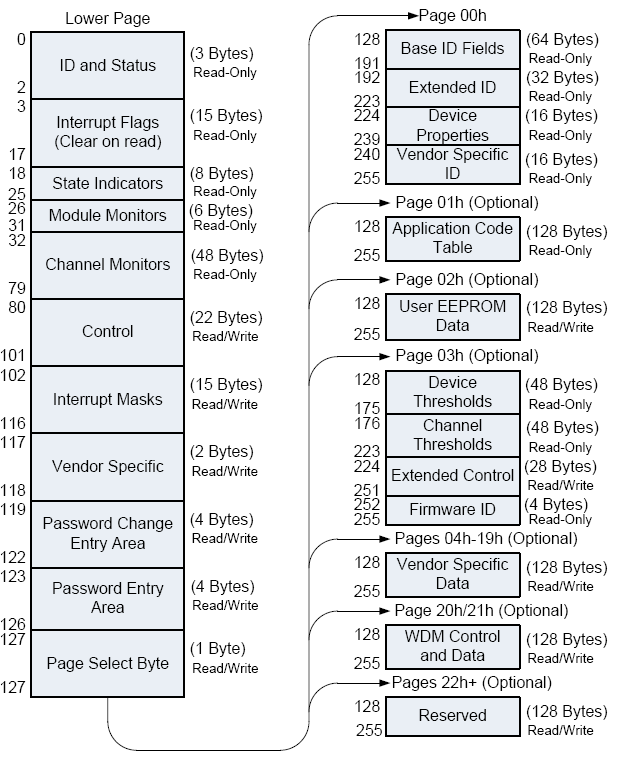

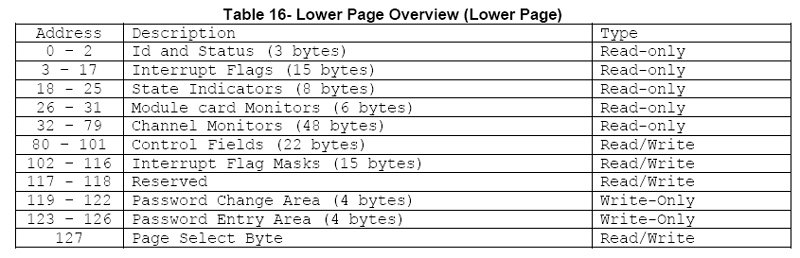

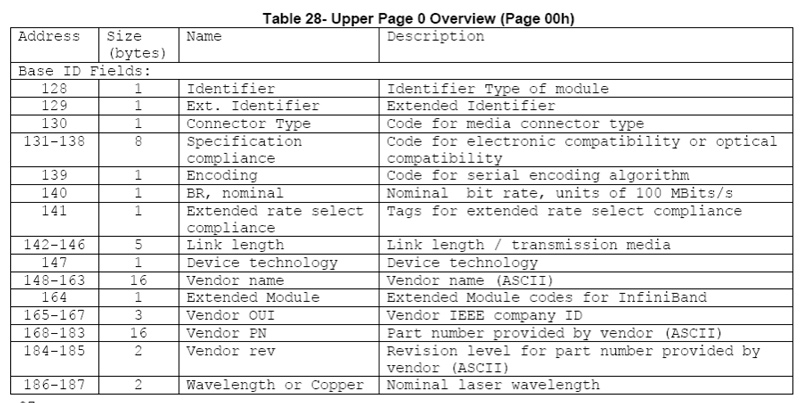

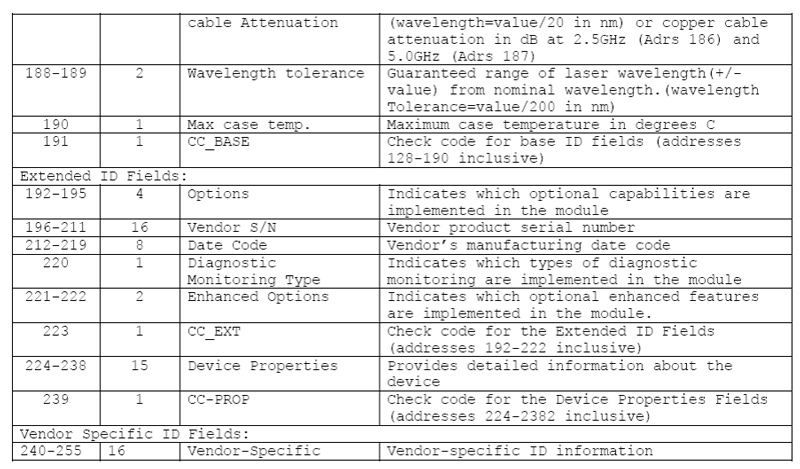

Die digitale Diagnose überwachungs funktion ist auf allen QSFP DD-Produkten verfügbar. Eine serielle 2-Draht-Schnitts telle bietet dem Benutzer Kontakt mit dem Modul. Die Struktur des Speichers ist in Abbildung 5 dargestellt. Der Speicher platz ist in einer unteren, einzelnen Seite, einem Adressraum von 128 Bytes und mehreren oberen Adressraum seiten angeordnet. Diese Struktur ermöglicht den rechtzeitigen Zugriff auf Adressen auf der unteren Seite, z. B. Interrupt Flags und Monitore. Weniger zeit kritische Einträge, z. B. serielle ID-Informationen und Schwellen werte in stellungen, sind mit der Funktion „ Seiten auswahl “verfügbar. Die Struktur bietet auch eine Adress erweiterung, indem bei Bedarf zusätzliche obere Seiten hinzugefügt werden. Die verwendete Schnitts telle adresse ist A0xh und wird haupt sächlich für zeit kritische Daten wie die Interrupt-Handhabung verwendet, um ein einmaliges Lesen für alle Daten zu ermöglichen, die sich auf eine Interrupt-Situation beziehen. Nachdem ein Interrupt, IntL, behauptet wurde, kann der Host das Flaggen feld auslesen, um den betroffenen Kanal und den Typ des Flags zu bestimmen.

Abbildung 5. QSFP DD Speicher karte

Abbildung 6. Niedrige Speicher karte

Figur 7. Seite 00 Speicher karte

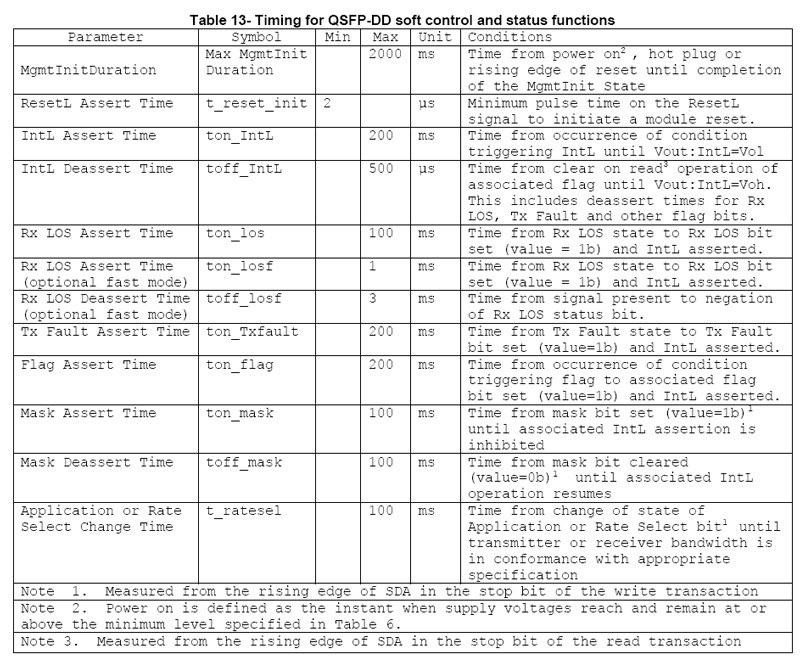

Timing für Soft Control-und Status funktionen

Abbildung 9. Timing-Spezifikationen

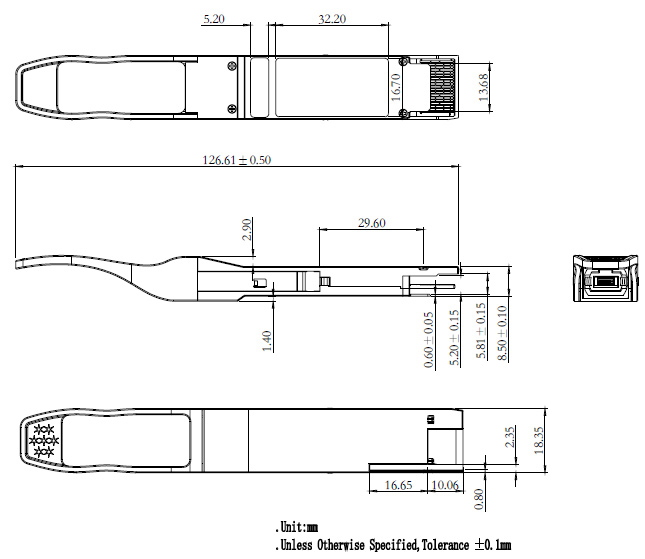

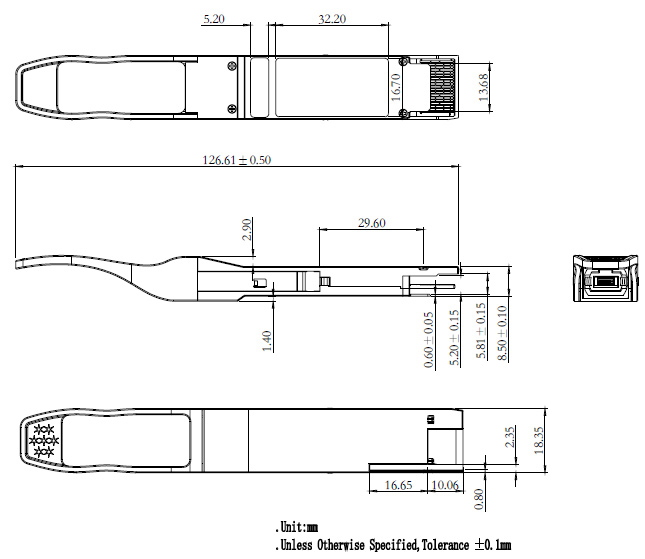

Umriss zeichnung (mm)

Absolute maximale Bewertungen

Parameter | Symbol | Min | Max | Einheit |

Versorgungs spannung | Vcc | -0,3 | 3.6 | V |

Eingangs spannung | Vin | -0,3 | Vcc + 0,3 | V |

Lagerte mperatur | Tst | -20 | 85 | °C |

Betriebs temperatur Fall | Top | 0 | 70 | °C |

Luft feuchtigkeit (nicht kondensierend) | Rh | 5 | 95 | % |

Empfohlene Betriebs bedingungen

Parameter | Symbol | Min | Typisch | Max | Einheit |

Versorgung Spannung | Vcc | 3.13 | 3.3 | 3.47 | V |

Betrieb Fall Temperatur | Tca | 0 |

| 70 | °C |

Datenrate Per Spur | Fd |

| 25.78125 |

| Gbps |

Luft feuchtigkeit | Rh | 5 |

| 85 | % |

Macht ableitung | Pm |

|

| 4 | W |

Elektrische Spezifikationen

Parameter | Symbol | Min | Typisch | Max | Einheit |

Differential Eingabe Impedanz | Zin | 90 | 100 | 110 | Ohm |

Differential Ausgabe Impedanz | Zout | 90 | 100 | 110 | Ohm |

Differential Eingangs spannung Amplitude AAmplitude | ΔVin | 300 |

| 1100 | MVp-p |

Differenz ielle Ausgabe Spannungs amplitude | ΔVout | 500 |

| 800 | MVp-p |

Versatz | Sw |

|

| 300 | Ps |

Bit-Fehlerrate | BER |

|

| 5E-5 |

|

Eingabe logik Niveau hoch | VIH | 2.0 |

| VCC | V |

Eingabe logik Niedriges Niveau | VIL | 0 |

| 0,8 | V |

Ausgabe logik Niveau hoch | VOH | VCC-0,5 |

| VCC | V |

Ausgabe logik Niedriges Niveau | VOL | 0 |

| 0.4 | V |

Anmerkung:

1. BER = 5E-5; PRBS 2 ^ 31-1 @ 25.78125Gbps. Pre-FEC

2. Differenz ielle Eingangs spannungs amplitude wird zwischen TxnP und TxnN gemessen.

3. Differenz ielle Ausgangs spannungs amplitude wird zwischen RxnP und RxnN gemessen.

Optische Eigenschaften

Tabelle 3-Optische Eigenschaften

Parameter | Symbol | Min | Typisch | Max | Einheit | Hinweise |

Sender |

Mittel wellenlänge | Λc | 840 | 850 | 860 | Nm | - |

RMS-Spektral breite | ∆Λ | - | - | 0,6 | Nm | - |

Durchschnitt liche Start leistung, Jede Spur | Schmellen | -8.4 | - | 2.4 | DBm | - |

Optische Modulation Amplitude (OMA), jede Spur | OMA | -6.4 |

| 3 | DBm | - |

Sender und Dispersion auge Schließung (TDEC), jede Spur | TDEC |

|

| 4.3 | DB |

|

Aussterbungs-Verhältnis | ER | 3 | - | - | DB | - |

Durchschnitt licher Start Macht des AUS Sender, Jede Spur |

|

|

| -30 | DB | - |

Augen maske Koordinaten: X1, X2, X3, Y1, Y2, Y3 | SPEZIFIKATIONS WERTE {0,3, 0,38, 0,45, 0,35, 0,41,0,5} | Treffer verhältnis = 5x10-5

|

Empfänger |

Mittel wellenlänge | Λc | 840 | 850 | 860 | Nm | - |

Gestresster Empfänger Empfindlichkeit in OMA |

|

|

| -5.2 | DBm | 1 |

Maximaler Durchschnitt Strom am Empfänger, Jede Spur Eingabe, jede Spur |

|

|

| 2.4 | DBm | - |

Mindest durchschnitt Strom am Empfänger, Jede Spur

|

|

|

| -10,3 | DBm |

|

Empfänger Reflexions vermögen |

|

|

| -12 | DB | - |

LOS Assert |

| -30 |

|

| DBm | - |

LOS De-Assert - OMA |

|

|

| -7.5 | DBm | - |

LOS-Hysterese |

| 0,5 |

|

| DB | - |

Anmerkung:

1. Gemessen mit Konformität tests ignal bei TP3 für BER = 5E-5 Per-FEC

Anwendungen

● IEEE 802.3bm 100GBASE SR4

Internet-Rechen zentrum

Internet-Rechen zentrum FAQs

FAQs Branchen nachrichten

Branchen nachrichten Über uns

Über uns Schalter für Rechen zentren

Schalter für Rechen zentren  Enterprise Switch

Enterprise Switch  Industrieller Schalter

Industrieller Schalter  Zugangs schalter

Zugangs schalter  Integriertes Netzwerk

Integriertes Netzwerk  Optisches Modul & Kabel

Optisches Modul & Kabel

Rufen Sie uns an:

Rufen Sie uns an:  Mailen Sie uns:

Mailen Sie uns:  2106B, # 3D, Cloud Park Phase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.

2106B, # 3D, Cloud Park Phase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.