Merkmale

● Bis zu 28Gbps Datenrate pro Kanal

● 8 Duplex kanäle Sender und Empfänger

● Integriertes 850-nm-VCSEL-Array und PD-Array

● Einzelne MPO24-Steckverbinder-Buchse optische Schnitts telle konform

● Einzelnes 3,3 V Netzteil

● DDM-Funktion implementiert

● Hot-plug able QSFP-DD Formfaktor

● Maximale Verbindungs länge von 100m auf 24 Kern MPO OM4 (MMF) Faser

● Verlust leistung: <4,5 W

● Internat ionale Klasse 1 Laser-Sicherheit zertifiziert

● Betriebs temperatur bereich: 0 ° c ~ 70

● Konform mit ROHS10

Absolute maximale Bewertungen

Parameter | Symbol | Einheit | Min | Max |

Lagerte mperatur bereich | Ts | ~ | -40 | 85 |

Relative Luft feuchtigkeit | RH | % | 5 | 95 |

Strom versorgungs spannung | Vcc | V | -0,5 | + 3.6 |

Empfohlene Betriebs bedingungen

Parameter | Symbol | Einheit | Min. | Typisch | Max |

Betriebs fall Temperatur bereich | Tc | ~ | 0 |

| 70 |

Strom versorgungs spannung | Vcc | V | 3.14 | 3.3 | 3.46 |

NRZ-Bit-Rate (pro Kanal) | BR | Gbps |

| 25.78 |

|

Optische Eigenschaften

Parameter | Symbol | Einheit | Min. | Typisch | Max | Hinweis |

Sender (pro Spur) |

Signal geschwindigkeit pro Spur |

| Gbps | 25.78125 | NRZ |

Wellenlänge im Zentrum |

| Nm | 840 | 850 | 860 |

|

RMS Spektral breite | SW | Nm |

|

| 0,6 |

|

Durchschnitt licher Start Leistung pro Spur | TXPx | DBm | -8.4 |

| 2.4 |

|

Tx OMA pro Spur | TxOMA | DBm | -6.4 |

| 3 |

|

Macht unterschied Zwischen Beliebig zweispurig (OMA) | DPx | DBm |

|

| 4 |

|

Durchschnitt liche Start leistung Des Off-Senders Pro Spur |

| DBm |

|

| -30 |

|

Sender und Dispersion Auge Sperrung pro Spur | TDEC | DB |

|

| 4.3 |

|

Start kraft in OMA minus TDEC |

| DBm | -7.3 |

|

|

|

Optisches Aussterben Verhältnis | ER | DB | 2 |

|

|

|

Optische Rückkehr Verlust Toleranz | ORL | DB |

|

| 12 |

|

Umkreist fluss | FLX | DBm | > 86% bei 19um |

|

<30% bei 4.5um |

|

Relative Intensität Lärm | RIN | DB/Hz |

|

| RIN |

|

Empfänger (pro Spur) |

Signal geschwindigkeit pro Spur |

| Gbps | 25.78125 | NRZ |

Wellenlänge im Zentrum |

| Nm | 840 |

| 860 |

|

Schadens schwelle | DT | DBm | 3.4 |

|

|

|

Durchschnitt licher Empfang Leistung pro Spur | RXPx | DBm | -10,3 |

| 2.4 |

|

Empfänger leistung (OMA) pro Spur | RxOMA | DBm |

|

| 3 |

|

Empfänger reflexions vermögen | Rfl | DB |

|

| -12 |

|

Vertikaler Augen verschluss Strafe, pro Spur |

| DB |

|

| 1.9 |

|

Gestresene Empfingen Empfindlichkeit (OMA) pro Spur | SRS | DBm |

|

| -5.2 |

|

Empfindlichkeit (OMA) pro Spur | S | DBm |

|

| -10,3 |

|

LOS De-Assert | LOSD | DBm |

|

| -12 |

|

LOS Assert | LOSA | DBm | -30 |

|

|

|

LOS-Hysterese |

| DBm | 0,5 |

|

|

|

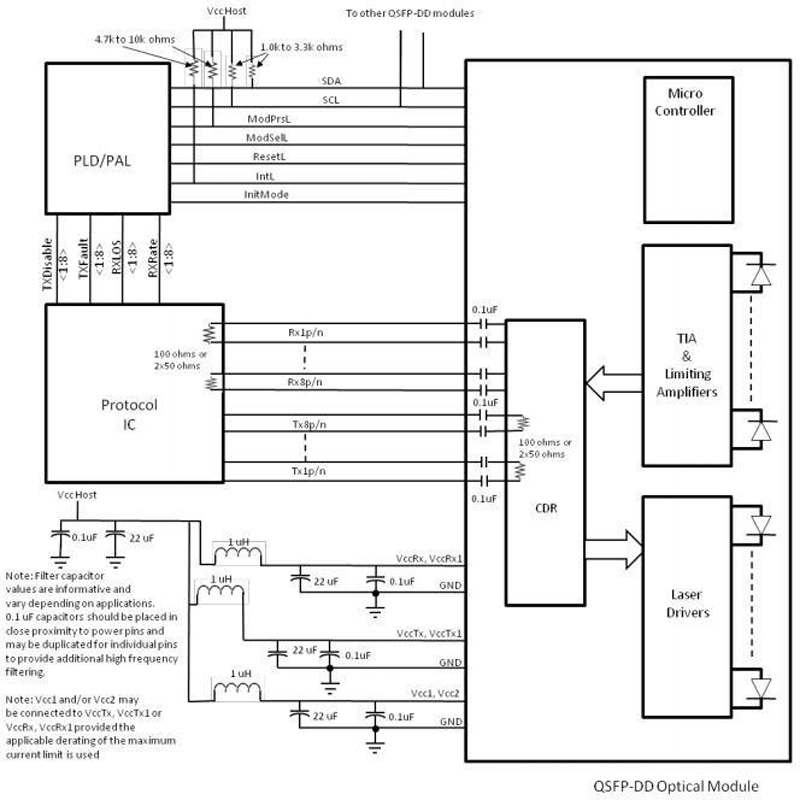

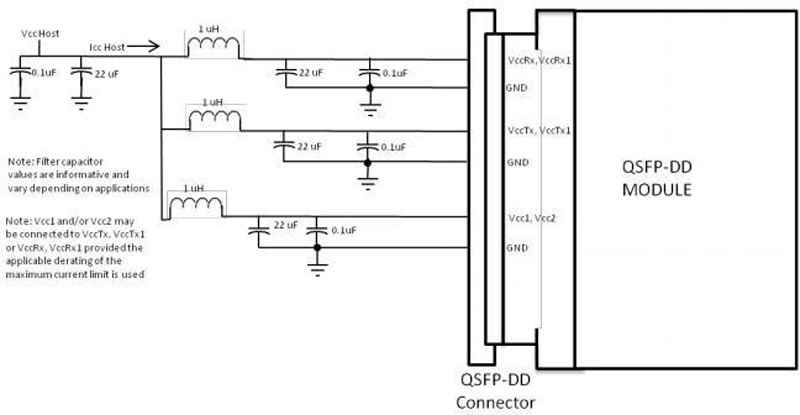

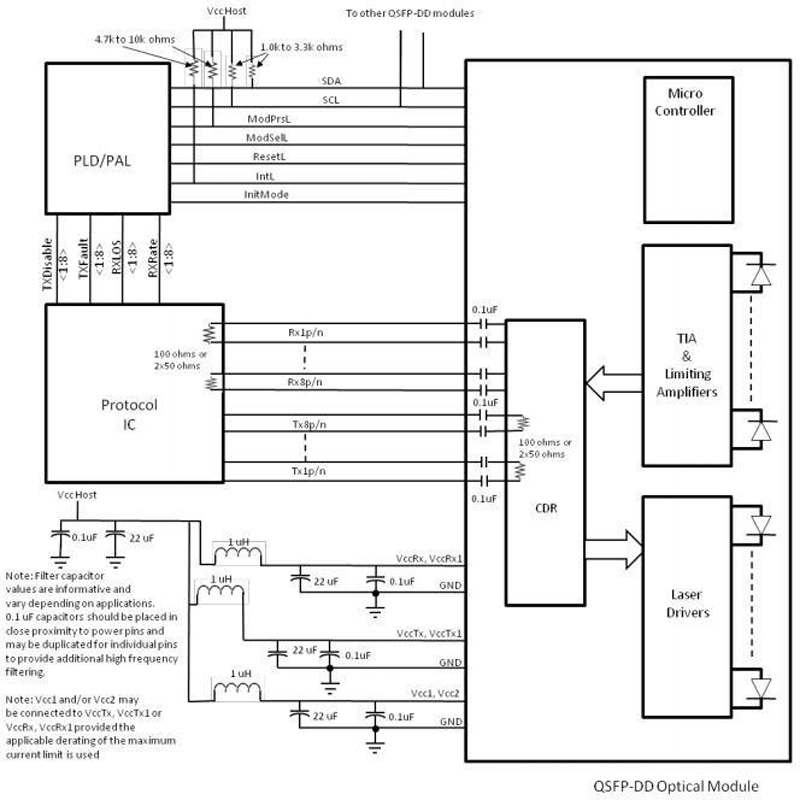

Grundsatz diagramm

Abbildung 1. Modul prinzip diagramm

Definition von elektrischen Häfen

Parameter | Symbol | Einheit | Min. | Typisch | Max | Hinweis |

Versorgungs spannung | VCC VCC 3.3-Tx VCC 3.3-Rx | V | 3.14 | 3.3 | 3.46 |

|

Versorgungs strom | Icc | MA |

|

| 1300 |

|

Strom verbrauch | Pc | W |

|

| 4.5 |

|

Transceiver Einschalten Zeit initial isieren |

| Ms |

|

| 2000 |

|

Sender |

Einendige Eingabe Volta Toleranz | VinT | V | -0,3 |

| 4.0 |

|

Different ielle Daten Eingangs schaukel |

VIN |

MVp-p |

300 |

|

1200 |

|

AC Common Modus ausgabe Spannung (RMS) |

| MV | 15 |

|

|

|

Differenz ielle Eingabe Impedanz |

| Ω | 90 | 100 | 110 |

|

Empfänger |

Einendige Eingabe Volta Toleranz | VoutR | V |

|

| 0.2 |

|

Different ielle Daten Ausgangs schaukel | Vout,PP | MVp-p | 350 |

| 850 |

|

AC-Gleichtakt Ausgangs spannung (RMS) |

| MV |

|

| 7.5 |

|

Differenz ielle Leistung Impedanz |

| Ω | 90 | 100 | 110 |

|

IIC-Kommunikation |

IIC Taktfrequenz |

| KHZ |

| 100 | 400 |

|

Uhr stretching |

| Uns |

|

| 500 |

|

Daten halte zeit |

| Ns | 300 |

|

|

|

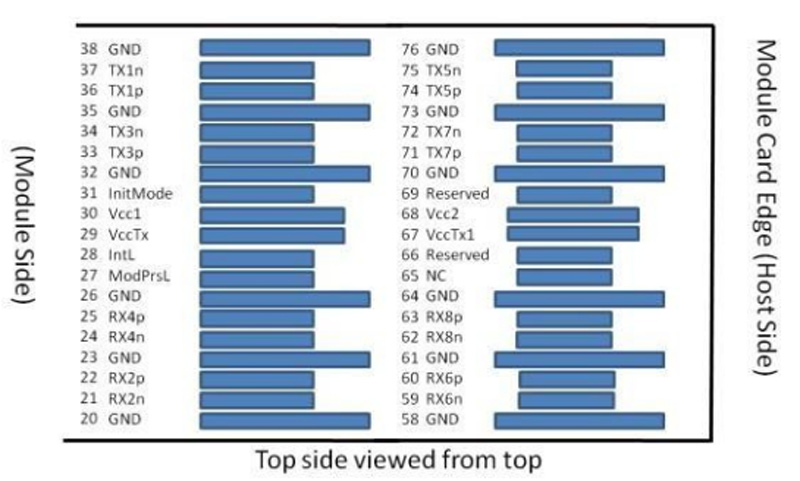

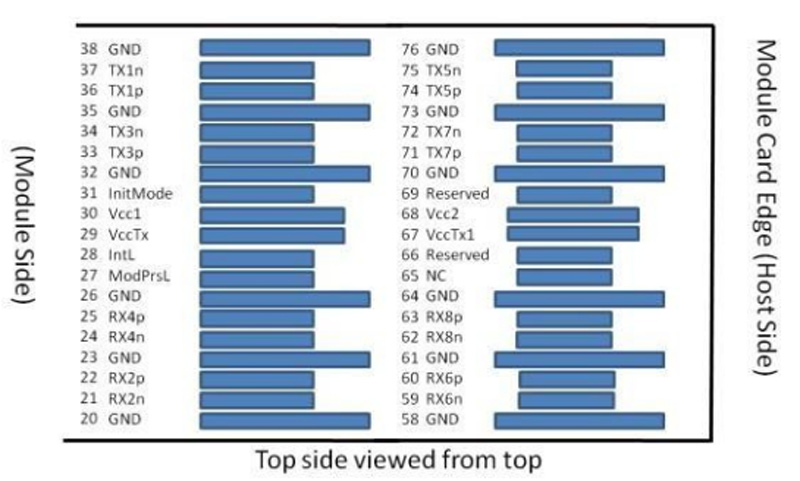

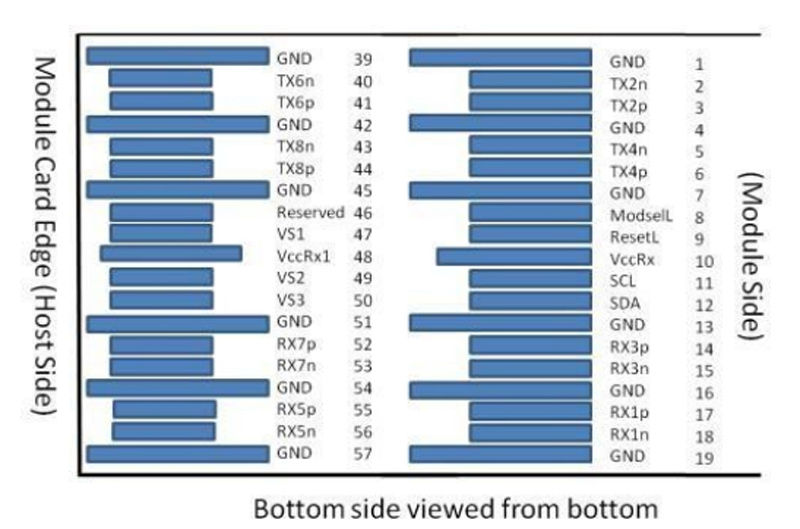

Pin Deion

Abbildung 2. Elektrische Pin-Out-Details

Pin | Logik | Symbol | Deion | Hinweis |

1 |

| Sc | Boden | 1 |

2 | CML-I | Tx2n | Transmitter Inverted Data Input |

|

3 | CML-I | Tx2p | Transmitter Non Inverted Data Input |

|

4 |

| Sc | Boden | 1 |

5 | CML-I | Tx4n | Transmitter Inverted Data Input |

|

6 | CML-I | Tx4p | Transmitter Non Inverted Data Input |

|

7 |

| Sc | Boden | 1 |

8 | LVTTL-I | ModSelL | ModuleS elect |

|

9 | LVTTL-I | ResetL | Modul Reset |

|

10 |

| VccRx | 3.3VPowerSupply-Empfänger | 2 |

11 | LVCOMS-I/O | SCL | 2-WireSerialInterfaceClock |

|

12 | LVCOMS-I/O | SDA | 2-WireSerialInterface Data |

|

13 |

| Sc | Boden | 1 |

14 | CML-0 | Rx3p | ReceiverNon-Inverted Data Output |

|

15 | CML-0 | Rx3n | Receiver Inverted Data Output |

|

16 |

| Sc | Boden | 1 |

17 | CML-0 | Rx1p | ReceiverNon-Inverted Data Output |

|

18 | CML-0 | Rx1n | Receiver Inverted Data Output |

|

19 |

| Sc | Boden | 1 |

20 |

| Sc | Boden | 1 |

21 | CML-0 | Rx2n | Receiver Inverted Data Output |

|

22 | CML-0 | Rx2p | ReceiverNon-Inverted Data Output |

|

23 |

| Sc | Boden | 1 |

24 | CML-0 | Rx4n | Receiver Inverted Data Output |

|

25 | CML-0 | Rx4p | ReceiverNon-Inverted Data Output |

|

26 |

| Sc | Boden | 1 |

27 | LVTTL-0 | ModPrsL | Modul present |

|

28 | LVTTL-0 | IntL | Unterbrechen |

|

29 |

| VccTx | 3.3VPowerSupply transmitter | 2 |

30 |

| Vcc1 | 3.3VPower Supply | 2 |

31 | LVTTL-I | InitMode | Initial isierungs modus; In LegacyQSFP-Anwendungen, theIntiModegadisc AlledLPMode |

|

32 |

| Sc |

Boden | 1 |

33 | CML-I | Tx3p | Transmitter Non Inverted Data Input |

|

34 | CML-I | Tx3n | Transmitter Inverted Data Input |

|

35 |

| Sc | Boden | 1 |

36 | CML-I | Tx1p | Transmitter Non Inverted Data Input |

|

37 | CML-I | Tx1n | Transmitter Inverted Data Input |

|

38 |

| Sc | Boden | 1 |

39 |

| Sc | Boden | 1 |

40 | CML-I | Tx6n | Transmitter Inverted Data Input |

|

41 | CML-I | Tx6p | Transmitter Non Inverted Data Input |

|

42 |

| Sc | Boden | 1 |

43 | CML-I | Tx8n | Transmitter Inverted Data Input |

|

44 | CML-I | Tx8p | Transmitter Non Inverted Data Input |

|

45 |

| Sc | Boden | 1 |

46 |

| Reserviert | Für die Zukunft | 3 |

47 |

| VS1 | ModuleVendorSpecific 1 | 3 |

48 |

| VccRx1 | 3.3VPowerSupply-Empfänger | 2 |

49 |

| VS2 | ModuleVendorSpecific 2 | 3 |

50 |

| VS3 | ModuleVendorSpecific 3 | 3 |

51 |

| Sc | Boden | 1 |

52 | CML-0 | Rx7p | ReceiverNon-Inverted Data Output |

|

53 | CML-0 | Rx7n | Receiver Inverted Data Output |

|

54 |

| Sc | Boden | 1 |

55 | CML-0 | Rx5p | ReceiverNon-Inverted Data Output |

|

56 | CML-0 | Rx5n | Receiver Inverted Data Output |

|

57 |

| Sc | Boden | 1 |

58 |

| Sc | Boden | 1 |

59 | CML-0 | Rx6n | Receiver Inverted Data Output |

|

60 | CML-0 | Rx6p | ReceiverNon-Inverted Data Output |

|

61 |

| Sc | Boden | 1 |

62 | CML-0 | Rx8n | Receiver Inverted Data Output |

|

63 | CML-0 | Rx8p | ReceiverNon-Inverted Data Output |

|

64 |

| Sc | Boden | 1 |

65 |

| NC | Not Connect | 3 |

66 |

| Reserviert | Für die Zukunft | 3 |

67 |

| VccTx1 | 3.3VPowerSupply transmitter | 2 |

68 |

| Vcc2 | 3.3VPower Supply | 2 |

70 |

| Sc | Boden | 1 |

71 | CML-I | Tx7p | Transmitter Non Inverted Data Input |

|

72 | CML-I | Tx7n | Transmitter Inverted Data Input |

|

73 |

| Sc | Boden | 1 |

74 | CML-I | Tx5p | Transmitter Non Inverted Data Input |

|

75 | CML-I | Tx5n | Transmitter Inverted Data Input |

|

76 |

| Sc | Boden | 1 |

Anmerkungen:

1.QSFP-DD nutzt für alle Signale und Versorgung (Strom) Common Ground (Falls). Alle Gemeinsamkeiten innerhalb des QSFP-DD Moduls und alle Moduls pannungen beziehen sich auf dieses Potential, sofern nicht anders angegeben. Verbundene Thesen direkt mit der Host-Platine signalisieren eine gemeinsame Erdung ebene.

2.VccRx, VccRx1, Vccc1, Vcc2, VccTx und VccTx1 sind gleichzeitig anzuwenden. Die für die Hosts eite des Host Card Edge Connectors definierten Anforderungen sind in Tabelle 4 aufgeführt. VccRx, VccRx1, Vccc1, Vcc2, VccTx und VccTx1 können intern in beliebiger Kombination innerhalb des Moduls verbunden sein. Die Stecker-Vcc-Pins sind jeweils für einen maximalen Strom von 1000mA ausgelegt.

3. Alle Anbieters pezi fischen, reservierten und No-Connect-Pins können mit 50 Ohm auf dem Host beendet werden. Pad 65 (No Connect) darf innerhalb des Moduls nicht anges ch lossen bleiben. Anbieters pezi fische und reservierte Pads müssen eine Impedanz gegenüber dem DNS haben, die größer als 10 kOhm und weniger als 100pF ist.

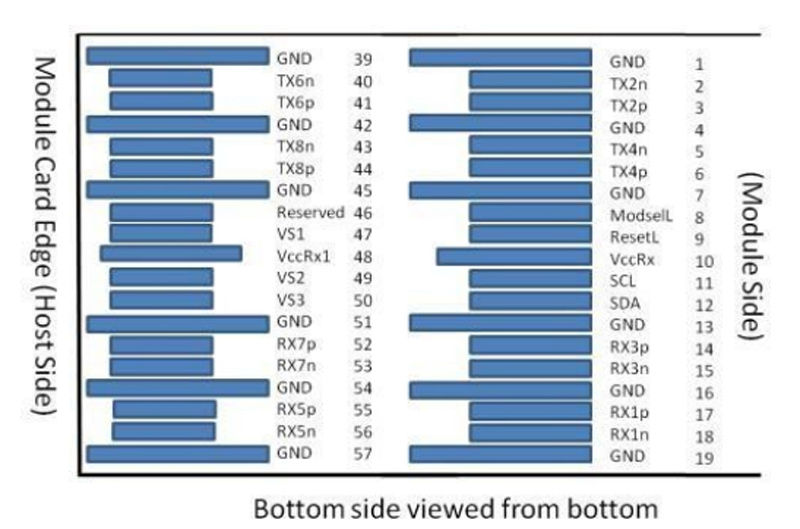

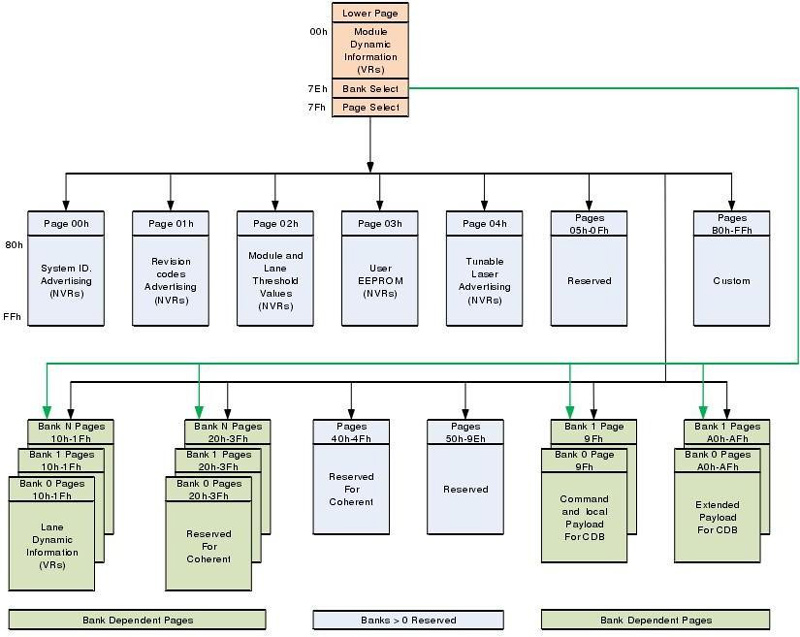

Digitale Diagnose speicher karte

Abbildung 3 Digitale Diagnose speicher karte

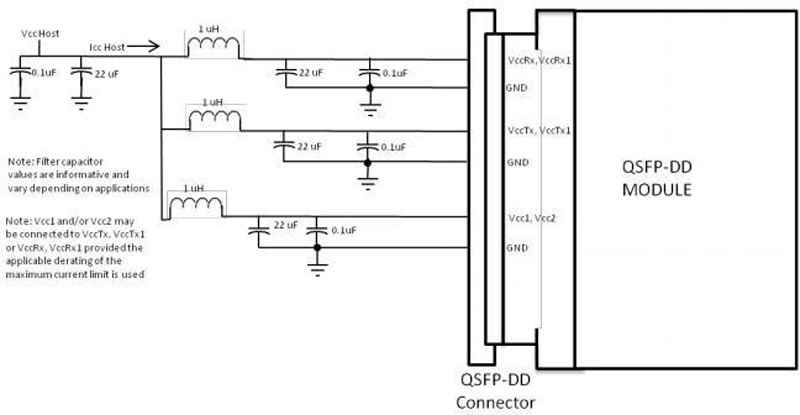

Host Board Netzteil Filterung

Jeder Spannungs abfall über ein Filter netzwerk auf dem Host wird auf die Spezifikation der Host-DC-Einstell genauigkeit angerechnet. Induktoren mit einem Gleichstrom widerstand von weniger als 0,1 Ohm sollten verwendet werden, um die erforderliche Spannung am Host Edge Card Connector aufrecht zu erhalten. Abbildung ist die vor geschlagene Transceiver/Host-Schnitts telle.

Abbildung 4 Empfohlene Host-Board-Strom versorgungs filterung

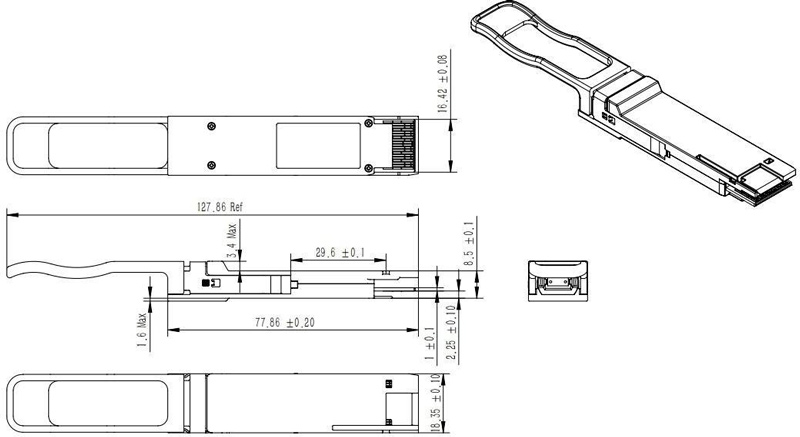

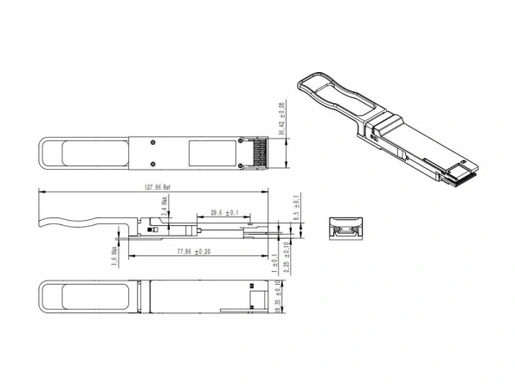

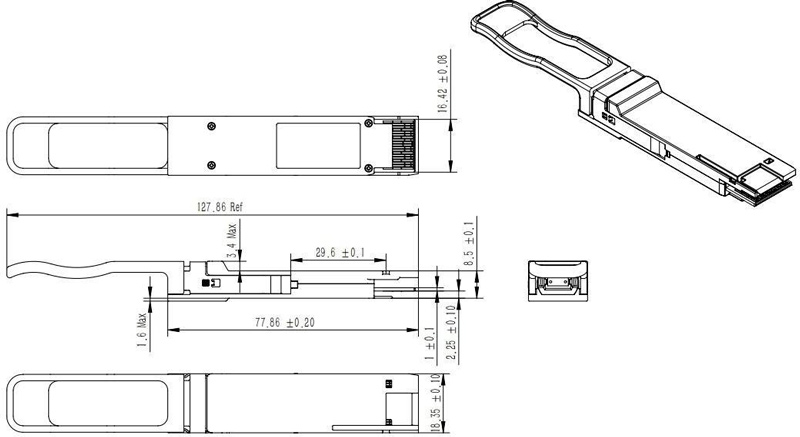

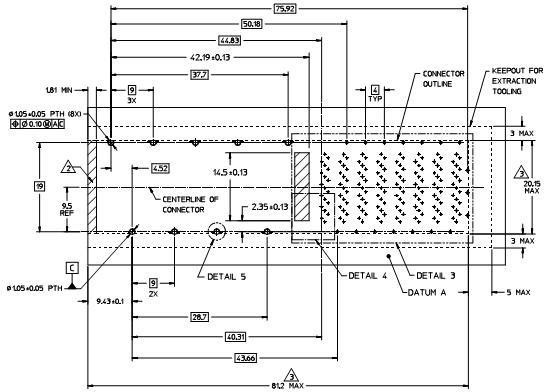

Umriss zeichnung (mm)

Abbildung 5 Paket übersicht

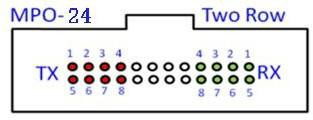

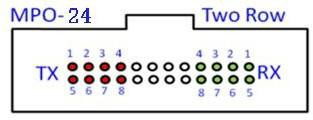

Abbildung 6 MPO Pinout Diagramm und Deion

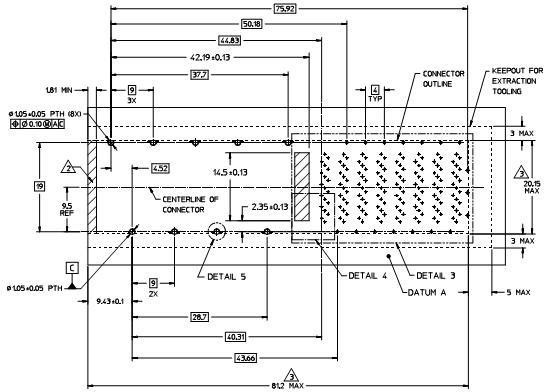

Empfehlung für das Host-PCB-Layout

Abbildung 7 PCB-Layout-Empfehlung

Anwendungen

● 200GBASE-SR8 Ethernet

● 2 × 100GBASE-SR4 Ethernet

● Switch & Router-Verbindungen

● Rechen zentren

● Andere 200G Verbindungs anforderungen

Internet-Rechen zentrum

Internet-Rechen zentrum FAQs

FAQs Branchen nachrichten

Branchen nachrichten Über uns

Über uns Schalter für Rechen zentren

Schalter für Rechen zentren  Enterprise Switch

Enterprise Switch  Industrieller Schalter

Industrieller Schalter  Zugangs schalter

Zugangs schalter  Integriertes Netzwerk

Integriertes Netzwerk  Optisches Modul & Kabel

Optisches Modul & Kabel

Rufen Sie uns an:

Rufen Sie uns an:  Mailen Sie uns:

Mailen Sie uns:  2106B, # 3D, Cloud Park Phase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.

2106B, # 3D, Cloud Park Phase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.